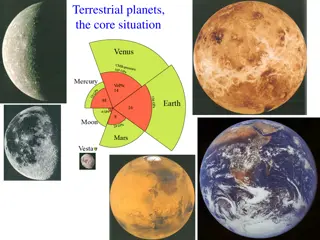

Terrestrial Planets and Core Dynamics

Exploring the core-mantle interaction from the early Hadean period to present times reveals intriguing questions about the outer core's electrical conductivity, geodynamo sustainability, and inner core characteristics. Studies indicate challenges in maintaining the geodynamo, potential heat sources

9 views • 48 slides

Multi-Head Attention Layers in Transformers

Sitan Chen from Harvard presents joint work with Yuanzhi Li exploring the provable learnability of a multi-head attention layer in transformers. The talk delves into the architecture of transformers, highlighting the gap between practical success and theoretical understanding. Preliminaries, prior w

3 views • 38 slides

Evolution of IBM System/360 Architecture and Instruction Set Architectures

The IBM System/360 (S/360) mainframe computer system family, introduced in 1964, revolutionized computing by offering forward and backward compatibility, a unified instruction set architecture (ISA), and a balance between scientific and business efficiency. The critical elements of this architecture

3 views • 18 slides

Shared Memory Architectures and Cache Coherence

Shared memory architectures involve multiple CPUs sharing one memory with a global address space, with challenges like the cache coherence problem. This summary delves into UMA and NUMA architectures, addressing issues like memory latency and bandwidth, as well as the bus-based UMA and NUMA shared m

2 views • 27 slides

IEEE 802.11-2020 Multi-Link Reference Model Discussion

This contribution discusses the reference model to support multi-link operation in IEEE 802.11be and proposes architecture reference models to support multi-link devices. It covers aspects such as baseline architecture reference models, logical entities in different layers, Multi-Link Device (MLD) f

3 views • 19 slides

IEEE 802.11-23/1980r1 Coordinated AP-assisted Medium Synchronization Recovery

This document from December 2023 discusses medium synchronization recovery leveraging multi-AP coordination for multi-link devices. It covers features such as Multi-link device (MLD), Multi-link operation (MLO), and Ultra High Reliability (UHR) capability defined in P802.11bn for improvements in rat

0 views • 8 slides

Shared Memory Architectures and Cache Coherence

Shared memory architectures involve multiple CPUs accessing a common memory, leading to challenges like the cache coherence problem. This article delves into different types of shared memory architectures, such as UMA and NUMA, and explores the cache coherence issue and protocols. It also highlights

2 views • 27 slides

Recertification and Assessment of Core Curriculum Courses

The Core Curriculum Council of the Faculty Senate presents a process for recertification and assessment of core curriculum courses to maintain integrity and quality. Courses must be recertified every four years to ensure consistency amidst changes in instructors, content, and teaching methods. State

0 views • 33 slides

Variations in Computer Architectures: RISC, CISC, and ISA Explained

Delve into the realm of computer architectures with a detailed exploration of Reduced Instruction Set Computing (RISC), Complex Instruction Set Computing (CISC), and Instruction Set Architecture (ISA) variations explained by Prof. Kavita Bala and Prof. Hakim Weatherspoon at Cornell University. Explo

2 views • 55 slides

Efficient Resource Management for Multi-Agent System Execution on Parallel Architectures with OpenCL

This research focuses on efficiently managing memory and computing resources for executing multi-agent systems on parallel architectures using OpenCL. The study presents a hybrid approach involving population-level molecular virtual chemistry and individual-level virtual cells. The work enhances a p

1 views • 33 slides

Research Insights on Future Internet Architectures

This survey explores key research topics in designing future internet architectures, focusing on innovations, content/data-oriented paradigms, mobility challenges, cloud-computing architectures, security considerations, and experimental testbeds. The study emphasizes the need for collaborative proje

0 views • 43 slides

Scaling Multi-Core Network Processors Without the Reordering Bottleneck

This study discusses the challenges in packet ordering within parallel network processors and proposes solutions to reduce reordering delay. Various approaches such as static mapping, single SN approach, and per-flow sequencing are explored to optimize processing efficiency in multi-core NP architec

0 views • 22 slides

Performance Aspects of Multi-link Operations in IEEE 802.11-19/1291r0

This document explores the performance aspects, benefits, and assumptions of multi-link operations in IEEE 802.11-19/1291r0. It discusses the motivation for multi-link operation in new wireless devices, potential throughput gains, classification of multi-link capabilities, and operation modes. The s

2 views • 30 slides

Embedded Computer Architecture - Instruction Level Parallel Architectures Overview

This material provides an in-depth look into Instruction Level Parallel (ILP) architectures, covering topics such as hazards, out-of-order execution, branch prediction, and multiple issue architectures. It compares Single-Issue RISC with Superscalar and VLIW architectures, discussing their differenc

1 views • 49 slides

Multi-Stage, Multi-Resolution Beamforming Training for IEEE 802.11ay

In September 2016, a proposal was introduced to enhance the beamforming training procedures in IEEE 802.11ay for increased efficiency and MIMO support. The proposal suggests a multi-stage, multi-resolution beamforming training framework to improve efficiency in scenarios with high-resolution beams a

1 views • 11 slides

Analysis of Transactional Memory Techniques in Multi-Core Architectures

Emerging multi-core architectures have led to the adoption of Transactional Memory (TM) as a new synchronization method. This study delves into the challenges of TM, examining the consequences of transaction aborts, the need for spare aborts, and evaluating measures to enhance transaction processing

0 views • 23 slides

OpenMP Programming on NUMA Architectures

In NUMA architectures, data placement and thread binding significantly impact application performance. OpenMP plays a crucial role in managing thread creation/termination and variable sharing in parallel regions. Programmers must consider NUMA architecture when optimizing for performance. This invol

1 views • 18 slides

Computer Systems and Operating System Architectures

An exploration of computer systems and operating system architectures, covering topics such as CPU modes, monolithic and layered architectures, microkernel architecture, Linux and Windows kernel architectures, as well as devices and their terminology. The content delves into the roles, structures, a

1 views • 57 slides

ASP.NET Core: Features, Ecosystem, and Differences

ASP.NET Core is a modern framework for building web applications with cross-platform capabilities. It offers a leaner and modular approach compared to ASP.NET Framework. With support for both .NET Core and full .NET Framework, ASP.NET Core enables developers to create applications that can run on Wi

2 views • 9 slides

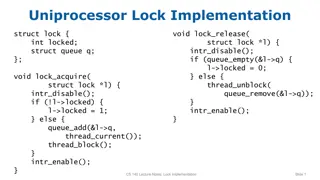

Lock Implementation Strategies for Single-Core and Multi-Core Systems

The provided content outlines several lock implementation strategies for both single-core and multi-core systems. It covers the structures, functions, and techniques used to manage locks efficiently, including releasing locks, acquiring locks, and handling synchronization. Different versions of lock

1 views • 6 slides

Discussion on Multi-AP Coordination Architecture in IEEE 802.11-23

In this document, Xiaofei Wang from InterDigital Communication Inc. discusses the architecture required for multi-AP operations, seamless roaming support, and general MLD operation support in the context of IEEE 802.11-23 standards. The focus is on coordinating various operations across multiple APs

0 views • 9 slides

Measurement-based WCET Analysis for Multi-core Architectures

This research focuses on providing an inexpensive multi-core solution for safety-critical systems by utilizing unmodified production chips and measurement-based WCET analysis tools. The goal is to enable WCET analysis on multi-core setups while preserving cost, performance, and time-to-market benefi

0 views • 25 slides

Efficient Hardware Architectures for Deep Neural Network Processing

Discover new hardware architectures designed for efficient deep neural network processing, including SCNN accelerators for compressed-sparse Convolutional Neural Networks. Learn about convolution operations, memory size versus access energy, dataflow decisions for reuse, and Planar Tiled-Input Stati

1 views • 23 slides

Multi-Processing in Computer Architecture

Beginning in the mid-2000s, a shift towards multi-processing emerged due to limitations in uniprocessor performance gains. This led to the development of multiprocessors like multicore systems, enabling enhanced performance through parallel processing. The taxonomy of Flynn categories, including SIS

0 views • 46 slides

Overview of DICOM WG21 Multi-Energy Imaging Supplement

The DICOM WG21 Multi-Energy Imaging Supplement aims to address the challenges and opportunities in multi-energy imaging technologies, providing a comprehensive overview of imaging techniques, use cases, objectives, and potential clinical applications. The supplement discusses the definition of multi

3 views • 33 slides

Performance Comparison of 40G NFV Environments

This study compares the performance of 40G NFV environments focusing on packet processing architectures and virtual switches. It explores host architectures, NFV related work, evaluation of combinations of PM and VM architectures with different vswitches, and the impact of packet processing architec

0 views • 24 slides

ACORN Core Outcomes Research Network Overview

ACORN (ACNE CORE OUTCOMES RESEARCH NETWORK) was established in July 2013 with the aim of creating a standardized set of core outcome measures for use in acne clinical trials. Led by key individuals such as Diane Thiboutot, Jerry Tan, and Alison Layton, ACORN focuses on global representation, stakeho

1 views • 10 slides

RESTful and Service-Oriented Architectures

Delve into the world of RESTful and Service-Oriented Architectures, exploring their components, constraints, and evolution over time. Learn about the Richardson Maturity Model and Resource-Oriented Architecture, and understand the key technologies and standards involved in building web services. Dis

0 views • 18 slides

11ay Functional Requirements for Multi-Hop, Backhaul, and Fronthaul

This document outlines the functional requirements for multi-hop transmissions in fronthaul and backhaul scenarios within the IEEE 802.11 TGay standard. It addresses the need for specific requirements in these use cases, proposing specifications to be included in the functional requirements document

0 views • 14 slides

Multi-Stage Transfer Learning System in Medical Image Classification

Transfer Learning is a deep learning technique that leverages pre-trained knowledge to improve learning in specific tasks. This study introduces a Multi-Stage Transfer Learning system with Lightweight architectures to address challenges like limited labeled data and computational costs in medical im

0 views • 18 slides

Distributed System Architectures: Software for Multiple Processors

Distributed system architectures involve designing software to run on multiple processors, optimizing resource sharing, openness, concurrency, scalability, fault tolerance, and transparency. These systems are crucial in today's world where most computer-based systems are distributed. Various types o

0 views • 61 slides

Understanding Vector Processing and SIMD Architectures in Modern CPUs

This content delves into the concept of vector processing and SIMD architectures in modern CPUs, focusing on Intel's instruction set extensions like MMX, SSE, AVX, and AVX512. It explains how SIMD architectures enable parallel processing of data, leading to enhanced performance for vector operations

0 views • 19 slides

Understanding Architectures in Distributed Systems

Explore the key concepts of architectures in distributed systems, including master-slave and peer-to-peer architectures. Learn about communicating entities, communication paradigms, roles, responsibilities, and organizational structures in distributed systems. Gain insights into the characteristics

0 views • 24 slides

Techniques for GPU Architectures with Processing-In-Memory Capabilities

Explore scheduling techniques for GPU architectures with processing-in-memory capabilities to enhance energy efficiency and performance. Delve into the challenges, advancements, and future prospects in the era of energy-efficient architectures. Identify bottlenecks such as off-chip transactions affe

0 views • 38 slides

Understanding Multi-Band Multi-Channel Concept in IEEE 802.11be

Explore the benefits and models of Multi-Band Multi-Channel (MBMC) operation in IEEE 802.11be, including efficient spectrum use, increased data rates, and dynamic band switching. Learn about single band vs. multi-band operation and different deployment scenarios for APs and non-AP STAs. Discover the

0 views • 20 slides

Multi-Core Processor Architectures and Scheduling Strategies

Explore the complexities of multi-processor scheduling in operating systems, including symmetric multiprocessing (SMP) and chip-multithreading (CMT). Learn about multicore processors, multithreaded systems, and the advantages of placing multiple cores on a single chip. Discover how modern processors

0 views • 20 slides

Understanding Information System Architectures and Services

Explore the intricate world of information system architectures and services, including the Model-View-Controller framework, managing complexity in distributed systems, service-oriented architectures, information institutions, libraries, and archives. Delve into the importance of information managem

1 views • 18 slides

Understanding Client/Server Architectures in Modern Database Management

Explore the concept of client/server architectures in database application development, covering networked computing models, application logic, application partitioning, and different types of client/server architectures such as File Server Architecture. Learn about the distribution of processing lo

0 views • 44 slides

Client/Server Architectures and Application Development Overview

Explore the world of database application development within client/server architectures. This comprehensive guide covers networked computing models, application logic in C/S systems, application partitioning, common logic distributions, and different types of client/server architectures. Learn abou

0 views • 39 slides

Understanding Abstraction in Computer System Architectures

Explore the concept of abstraction in computer system architectures beyond the common function units. Delve into von Neumann, Harvard, and Dataflow architectures to understand how data and instructions are stored and processed differently. Gain insights into the fundamental principles shaping comput

0 views • 22 slides