Understanding MIPS Part II: Memory Organization and Instructions

Explore the intricacies of Memory Organization in the context of MIPS architecture, covering topics such as Memory Transfer Unit, Word Alignment, Load and Store Instructions, Making Decisions with Conditional Branching and Unconditional Jumps, Loops, Arrays and practical exercises. Learn about the m

16 views • 43 slides

727003-B21 HP BL460C G9 E5-2695 V3 14-CORE PROCESSOR KIT

Refurbished | HP 727003-B21 | BL460C G9 E5-2695 V3 14-CORE PROCESSOR KIT | \u2713 FREE and FAST Ground Shipping across the U.S. | Best Price Guaranteed\n\n\/\/ \/727003-b21-hp-bl460c-g9-e5-2695-v3-14-core-processor-kit\/

0 views • 1 slides

Understanding Cache and Virtual Memory in Computer Systems

A computer's memory system is crucial for ensuring fast and uninterrupted access to data by the processor. This system comprises internal processor memories, primary memory, and secondary memory such as hard drives. The utilization of cache memory helps bridge the speed gap between the CPU and main

1 views • 47 slides

Understanding Superscalar Processors in Processor Design

Explore the concept of superscalar processors in processor design, including the ability to execute instructions independently and concurrently. Learn about the difference between superscalar and superpipelined approaches, instruction-level parallelism, and the limitations and design issues involved

0 views • 55 slides

MIPS CPU Design Using Verilog and Instruction Set Architecture Overview

Explore the world of MIPS CPU design using Verilog with a deep dive into Instruction Set Architecture (ISA), SPIM instruction formats, addressing modes, and more. Learn about the key components such as Program Counter (PC), Instruction Memory (IM), Register Files (RF), Arithmetic Logic Unit (ALU), D

1 views • 29 slides

Understanding Basic Input/Output Operations in Computer Organization

Basic Input/Output Operations are essential functions in computer systems that involve transferring data between processors and external devices like keyboards and displays. This task requires synchronization mechanisms due to differences in processing speeds. The process involves reading characters

0 views • 11 slides

Buy 872012-B21 HPE BL460C GEN10 XEON-S 4110 PROCESSOR KIT

Refurbished | HPE 872012-B21 | BL460C GEN10 XEON-S 4110 PROCESSOR KIT | \u2713 FREE and FAST Ground Shipping across the U.S. | Best Price Guaranteed\n\n\/\/ \/872012-b21-hpe-bl460c-gen10-xeon-s-4110-processor-kit\/

0 views • 1 slides

Processor Control Unit and ALU Implementation Overview

In Chapter 4, the processor's control unit and ALU are detailed in a simple implementation scheme. The ALU performs operations based on opcode values, while the control unit provides signals for various functions such as load/store, compare, and branch. Decoding techniques and control signal generat

1 views • 21 slides

Overview of MIPS Arithmetic and Logic Instructions in COE 301

MIPS Architecture consists of R-Type and I-Type instruction formats for arithmetic, logical, shift, and immediate constant operations. It includes a variety of general-purpose registers and specific units for execution, floating-point operations, and memory handling. The presentation outlines the st

2 views • 29 slides

Understanding Instruction Set Architecture and Data Types in Computer Systems

In computer architecture, the Instruction Set Architecture (ISA) level is crucial in defining how a processor executes instructions. This includes the formal defining documents, memory models, registers, and various data types that can be supported. The ISA level specifies the capabilities of a proc

2 views • 13 slides

Understanding Computer System Architectures

Computer systems can be categorized into single-processor and multiprocessor systems. Single-processor systems have one main CPU but may also contain special-purpose processors. Multiprocessor systems have multiple processors that share resources, offering advantages like increased throughput, econo

2 views • 25 slides

Techniques for Reducing Connected-Standby Energy Consumption in Mobile Devices

Mobile devices spend a significant amount of time in connected-standby mode, leading to energy inefficiency in the Deepest-Runtime-Idle-Power State (DRIPS). This study introduces Optimized DRIPS (ODRIPS) to address this issue by offloading wake-up timer events, powering off IO signals, and transferr

1 views • 31 slides

Understanding Processor Interrupts and Exception Handling in Zynq Systems

Learn about interrupts, exceptions, and their handling in Zynq Systems. Explore concepts like interrupt sources, Cortex-A9 processor interrupts, interrupt terminology, and the difference between pooling and hardware interrupts. Gain insights into interrupt service routines, interrupt pins, interrupt

0 views • 60 slides

Performance Analysis of Different MIPS Processors

This analysis compares two different implementations (P1 and P2) of the same instruction set based on clock rates, CPI values, peak performances, and execution times on a 3GHz MIPS processor. The performance trade-offs for changes made to an MIPS process are explored using a breakdown of different p

0 views • 42 slides

MIPS Single-cycle Datapath Analysis for Instruction SW

Examine the operation of the single-cycle datapath for a specific MIPS instruction "SW.R4,-100(R16)". This analysis covers the instruction word value, register numbers, control signals, and the logic diagram implementation. Dive into details like instruction word encoding, register file operations,

0 views • 55 slides

In-Depth Look at Pentium Processor Features

Explore the advanced features of the Pentium processor, including separate instruction and data caches, dual integer pipelines, superscalar execution, support for multitasking, and more. Learn about its 32-bit architecture, power management capabilities, internal error detection features, and the ef

0 views • 24 slides

Trends in Computer Organization and Architecture

This content delves into various aspects of computer organization and architecture, covering topics such as multicore computers, alternative chip organization, Intel hardware trends, processor trends, power consumption projections, and performance effects of multiple cores. It also discusses the sca

5 views • 28 slides

Understanding Pipelined Control in Processor Architecture

Explore the intricacies of pipelined control in processor design, detailing the control signals required at each stage of the pipeline. Learn about data hazards, forwarding, and stalling techniques to ensure efficient instruction execution. Dive into the concept of optimized control values for strea

0 views • 16 slides

Understanding Branching and Condition Codes in Computer Architecture

Explore the intricacies of branching statements, if-else statements, condition codes, explicit compare and branch, implicit condition codes, and the use of condition registers in computer architecture. Delve into MIPS architecture's utilization of both implicit and condition registers for efficient

0 views • 16 slides

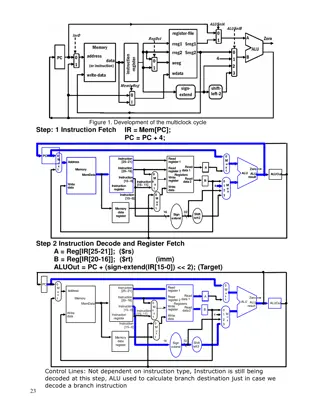

Development of Multiclock Cycle in Processor

The development process of the multiclock cycle in a processor is explained in detail through different steps, including instruction fetch, decode, register fetch, execution, and write-back for R-type instructions. Control lines and branching execution are also covered in the description. The conten

0 views • 5 slides

Overview of Inter-Processor Communication (IPC) in Processor Communication Link

Overview of Inter-Processor Communication (IPC) entails communication between processors, synchronization methods, and supported device types. The IPC architecture supports diverse use cases with various thread combinations and messaging types, catering to multi- or uni-processor environments. The A

0 views • 110 slides

Understanding RISC, CISC, and ISA Variations in Computer Science

Explore the differences between RISC and CISC architectures, along with variations in Instruction Set Architecture (ISA). Dive into the intricacies of processor design, performance factors, and assembly languages. Get insights into the concepts of control units, memory units, pipelines, and datapath

0 views • 37 slides

Understanding MIPS I/O and Interrupt Handling

Delve into the world of MIPS architecture, exploring how I/O operations and interrupts are managed. Learn about memory organization, system functions, I/O registers, and kernel data. Discover how SPIM facilitates input and output handling, including reading from the keyboard and managing output. Div

0 views • 18 slides

Understanding MIPS Instruction Sets and Binary Execution

This lecture covers the mapping of MIPS instructions to binary for execution, the use of pseudo-instructions to improve code readability, and the handling of large constants. It discusses levels of representation and interpretation, the concept of stored-program computers, addressing in memory, bina

0 views • 50 slides

Out-of-Order Processor Design Exploration

Explore the design of an Out-of-Order (OOO) processor with an architectural register file, aggressive speculation, and efficient replay mechanisms. Understand the changes to renaming, dispatch, wakeup, bypassing, register writes, and commit stages. Compare Processor Register File (PRF) based design

0 views • 29 slides

Understanding MIPS Functions and Calling Conventions

MIPS functions in assembly language are called using the 'jal' instruction, passing arguments in specific registers. Functions must end with 'jr $ra' and have explicit declarations. MIPS functions are stored separately from the main function in memory. The 'jal' instruction jumps to a specified addr

0 views • 18 slides

Understanding Processor Cycles and Machine Cycles in 8085 Microprocessor

Processor cycles in microprocessors like 8085 involve executing instructions through machine cycles that are essential operations performed by the processor. In the 8085 microprocessor, there are seven basic machine cycles, each serving a specific purpose such as fetching opcodes, reading from memor

0 views • 17 slides

Introduction to MIPS Assembly Programming with MARS

Introduction to MIPS Assembly Programming with MARS including instructions, I-Type format, register initialization, addi instructions, and translation to machine code using an assembler. Learn how to perform basic arithmetic operations in MIPS assembly language.

0 views • 61 slides

Understanding MACRA and MIPS for Post-Acute Care Providers

Explore the key provisions of MACRA impacting post-acute care (PAC) providers, including the Merit-based Incentive Payment System (MIPS) and Advanced Alternative Payment Models (APMs). Learn about quality reporting requirements, payment structures, and participation options under MACRA to optimize r

0 views • 20 slides

Understanding MIPS Arithmetic Logic Unit (ALU)

The MIPS ALU is the heart of computer calculations, performing functions like add, and, or, and sub. This article delves into designing a full ALU, starting from a 1-bit full adder to a 32-bit ALU. It explores how operations like and, or, and addition are carried out within the ALU, and how to imple

0 views • 28 slides

Exception Handling and Interrupts in MIPS Architectures

Exception and interrupts in MIPS play a crucial role in handling unexpected events and external requests efficiently. Exceptions include changes in control flow, arithmetic overflows, and hardware malfunctions, while interrupts are externally caused events like I/O requests. When an exception occurs

1 views • 29 slides

Understanding Computer Architecture: Exploring MIPs, Assembly Code, and BIOS Functions

Dive into the world of computer architecture with a focus on MIPs assembly language, basic program formats, BIOS functions, and system calls. Learn about the role of the OS kernel, memory addresses, and control flow in executing programs efficiently.

0 views • 16 slides

Understanding Processor Organization in Computer Architecture

Processor organization involves key tasks such as fetching instructions, interpreting instructions, processing data, and storing temporary data. The CPU consists of components like the ALU, control unit, and registers. Register organization plays a crucial role in optimizing memory usage and control

0 views • 21 slides

Understanding Processor Structure and Function in Computing

Explore the key components and functions of processors in computing, including user-visible and control status registers, instruction cycle, instruction pipelining, processor tasks like data processing and instruction interpretation, and the roles of arithmetic and logic units and control units. Lea

0 views • 61 slides

Understanding Computer Organization and Memory Management

Explore the fundamentals of computer organization, memory organization, and execution of instructions in a processor. Learn about memory addressing, word lengths, byte organization, and access methods. Understand the role of registers in the control path for instruction execution. Delve into MIPS la

0 views • 37 slides

Overview of Single-Cycle Implementation in Computer Organization

Today's lecture discussed the single-cycle implementation of processors, focusing on executing instructions in hardware based on the ISA. The process involves different cycles such as instruction fetch, decode, execution, memory access, and write-back. The presentation highlighted the functions of a

0 views • 24 slides

Understanding Processor Generations and VM Sizing for Azure Migration

Exploring the impact of processor generations on CPU performance, factors like clock speed, instruction set, and cache size are crucial. Choosing the right-sized VM plays a vital role in optimizing Azure migration. Passmark CPU Benchmark results provide insights on Intel processor generations for Az

0 views • 9 slides

MIPS 2022 Updates and Program Recap for Large Practices

Explore the latest updates for the Merit-Based Incentive Payment Program (MIPs) in 2022, including performance year changes, quality category considerations, penalty mitigation strategies, and historical thresholds. Learn how MIPS rewards clinicians for high-quality, cost-effective care under MACRA.

0 views • 27 slides

Understanding Context Switching and User-Kernel Interaction in Operating Systems

Context switching in operating systems involves a seamless transition between user-level threads without the kernel's awareness. User-level code manages register state and stack pointers, while user-kernel mode switching requires changing processor privilege levels and agreement on information excha

0 views • 25 slides

Understanding Instruction Set Architectures (ISAs) in Computer Science

Explore the concepts of RISC, CISC, and ISA variations in computer architecture. Dive into the differences between MIPS, ARM, X86, and other ISAs, focusing on load/store, arithmetic, control flow, and more. Gain insights into the evolution and variations of ISAs, and discover the alternatives beyond

0 views • 37 slides