Enhancing QoS Facility for Low-Latency High-Throughput Performance in IEEE 802.11 Networks

This proposal addresses the shortcomings in traffic classification and handling of uplink/downlink traffic in current IEEE 802.11 specifications, particularly in relation to low-latency traffic. It also highlights issues with the current EDCA mode in managing congestion and proposes high-level solut

5 views • 18 slides

Understanding Latency in Sentinel-1A Standard Products

The provided information delves into the latency definitions and averages related to ESA Sentinel-1A Standard Products. It covers the different product types, including Extra Wide (EW), Interferometric Wide (IW), and Wave (WV), detailing the average latencies at various stages in data processing. La

5 views • 20 slides

Enhanced Scheduling Method for Low Latency Traffic in IEEE 802.11-24/0091r1

This document presents an enhanced scheduling method for handling low latency traffic in IEEE 802.11 networks. It focuses on supporting deterministic and event-based latency-sensitive traffic, addressing challenges in scheduling and resource allocation. The proposed method aims to improve the reliab

8 views • 12 slides

Enhancing Low Latency Channel Access in Legacy IEEE 802.11 Networks

This document discusses the impact of introducing a Low Latency (LL) channel access mechanism in legacy IEEE 802.11 networks. It addresses the use of High Priority EDCA (HiP EDCA) mechanisms, proposing solutions for improving tail latency in both isolated BSS and multi-BSS scenarios. Additionally, i

2 views • 10 slides

Two-Dimensional A-PPDU for Low Latency in UHR Networks

This document discusses the proposed two-dimensional (2D) A-PPDU as a solution for supporting low-latency applications in UHR networks. It delves into the details of 2D A-PPDU for downlink, focusing on the ability to insert PPDUs within a PPDU, aiming to reduce latency in UHR environments by enhanci

0 views • 17 slides

Gradual Fine-Tuning for Low-Resource Domain Adaptation: Methods and Experiments

This study presents the effectiveness of gradual fine-tuning in low-resource domain adaptation, highlighting the benefits of gradually easing a model towards the target domain rather than abrupt shifts. Inspired by curriculum learning, the approach involves training the model on a mix of out-of-doma

0 views • 17 slides

Improving Low-Latency Buffer Status Reporting in IEEE 802.11

Proposal for enhancing the Buffer Status Report (BSR) mechanism in IEEE 802.11 to include timing constraints for transmitting latency-sensitive traffic. Suggestions involve adding TSPEC-based signaling and efficient mechanisms for Enhanced Traffic APs to ascertain low-latency traffic status. The cur

0 views • 12 slides

Analyzing and Improving Latency in IEEE 802.11 Networks

The document discusses controlling latency in IEEE 802.11 networks to meet the demands of emerging applications that require not only high throughput but also low latency. It covers aspects such as latency analysis, potential improvements, latency vs. reliability trade-offs, and latency improvement

4 views • 14 slides

Evaluation of Low-Latency Services in IEEE 802.11-23/1530r1

This document discusses the evaluation of supported low-latency services in the context of IEEE 802.11-23/1530r1, focusing on the reliability of WLAN, throughput, latency, and MPDU loss. It addresses the challenges in supporting new low-latency services such as AR/VR and industrial IoT, particularly

1 views • 11 slides

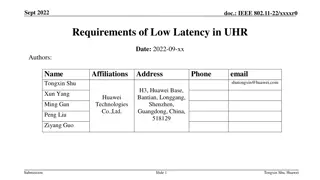

Low Latency Requirements in Ultra-High Rate Communication

This document discusses the requirements and use cases of low latency in ultra-high rate communication scenarios, highlighting applications such as metaverse, cloud gaming, real-time video streaming, in-vehicle infotainment, and industrial PLC control. It also covers current methods to reduce latenc

1 views • 12 slides

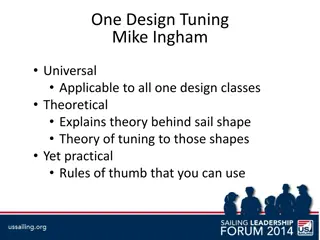

One Design Tuning Tips for Sail Shape and Mast Bend

Explore the theoretical explanations and practical rules of tuning sail shape and mast bend in one design sailing classes. Learn about achieving balance, controlling helm, adjusting forestay rake, shaping the sail, bending the mast, and tuning mast bend for/aft to optimize performance on the water.

0 views • 23 slides

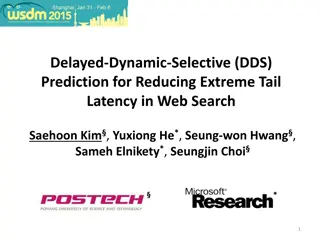

Enhancing Web Search Latency with DDS Prediction

This presentation delves into DDS Prediction, a technique designed to reduce extreme tail latency in web search engines by optimizing query execution times and parallelizing specific queries. It addresses the challenges of improving latency for all users and emphasizes the importance of achieving hi

0 views • 31 slides

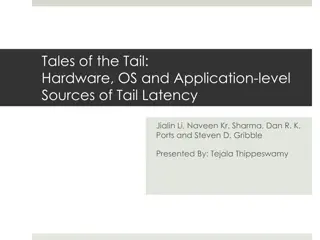

Understanding Sources of Tail Latency in Hardware, OS, and Applications

Delve into the impact of latency on revenue, with real-world examples from companies like Amazon and Google. Explore the complexities of achieving low tail latency in large-scale applications and the approach to analyzing and mitigating latency sources at hardware, OS, and application levels.

0 views • 24 slides

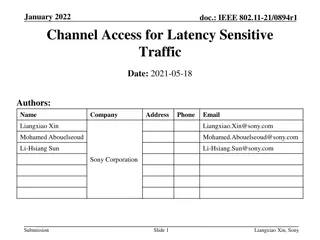

Enhancing Channel Access for Latency-Sensitive Traffic in January 2022

In the documentation IEEE 802.11-21/0894r1, the focus is on improving channel access for latency-sensitive traffic through concepts like Restricted TWT (Target Wake Time). The proposal suggests methods to protect TWT Service Periods from non-TWT scheduled STAs, ensuring prioritized transmission of l

0 views • 11 slides

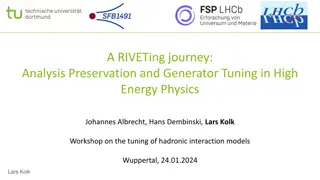

Enhancing High Energy Physics Research Through Analysis Preservation and Generator Tuning

Delve into the world of high-energy physics with a riveting journey through the analysis preservation and tuning of hadronic interaction models. Learn about the motivation, goals, and processes involved in making research results accessible, publicly available, and reproducible. Explore the tools an

0 views • 23 slides

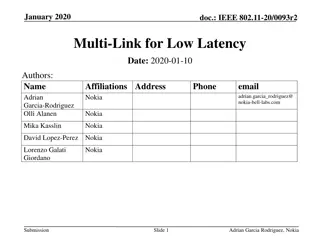

Enhancing Efficiency and Latency Reduction in IEEE 802.11be Through Multi-Link Operation

Targeted at improving multi-link and low-latency capabilities in IEEE 802.11be, this document proposes a mode of operation utilizing multiple links to decrease latency effectively. By addressing channel access delay reduction and discussing the benefits of multi-link definitions, the document emphas

0 views • 17 slides

Architecting DRAM Caches for Low Latency and High Bandwidth

Addressing fundamental latency trade-offs in designing DRAM caches involves considerations such as memory stacking for improved latency and bandwidth, organizing large caches at cache-line granularity to minimize wasted space, and optimizing cache designs to reduce access latency. Challenges include

0 views • 32 slides

Managing DRAM Latency Divergence in Irregular GPGPU Applications

Addressing memory latency challenges in irregular GPGPU applications, this study explores techniques like warp-aware memory scheduling and GPU memory controller optimization to reduce DRAM latency divergence. The research delves into the impact of SIMD lanes, coalescers, and warp-aware scheduling on

0 views • 33 slides

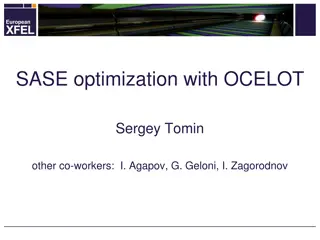

SASE Optimization with OCELOT: Recent Advances and Results

OCELOT, along with fellow researchers, has been optimizing SASE at facilities like FLASH, focusing on economic benefits and improved performance. By combining model-free and model-depending optimization techniques, they have achieved significant progress in beam dynamics simulations and tuning seque

0 views • 30 slides

Impact of Latency on Player Performance in Cloud-based Games

Research conducted by Mark Claypool and David Finkel explores the effects of latency on player performance in cloud-based games. The study compares the impact of latency on both objective (performance) and subjective (quality) measures, highlighting how every 100ms increase in latency results in a 2

0 views • 21 slides

Enhancing Low Latency in IEEE 802.11 Networks

Various mechanisms for low latency in IEEE 802.11 networks are discussed, including C-TDMA, C-RTWT, TXOP Preemption, and HiP-EDCA. This proposal aims to improve initial control frame exchanges to prioritize low latency traffic transmission. By modifying exchange rules and allowing STAs to signal the

0 views • 12 slides

Low-Latency Inter-Datacenter State Machine Replication Using Clock-RSM

Clock-RSM introduces a low-latency approach to inter-datacenter state machine replication by utilizing loosely synchronized physical clocks. This method ensures strong consistency, fault tolerance, and fast failover in a geo-replication environment. By overlapping ordering and replication using phys

0 views • 29 slides

Streamlining Job Performance Through Automated Tuning Processes

Explore the innovative approach of Tuning to enhance job performance while sleeping. Learn about the vision, mission, architecture, and typical conversations related to this process. Discover the significance of tuning, manual tuning phases, and Dr. Elephant's heuristic-based recommendations for opt

0 views • 36 slides

Machine Learning Optimization for HTTP Latency Tuning on NGINX

Exploration of machine learning optimization algorithms for enhancing HTTP latency tuning on NGINX. The study investigates the use of ML tuning as a superior alternative to manual methods, focusing on operating system tuning, existing methods, and future autotuning work. Key areas covered include me

0 views • 24 slides

Comprehensive Guide to Bow Tuning and Equipment Workshops 2019-2020

Delve into the world of bow tuning and equipment workshops with this detailed guide. Learn about bareshaft tuning, arrow spine, arrow flight behavior, and more essential topics for archery enthusiasts. Discover methods to ensure consistent technique and optimize your equipment setup for a fulfilling

0 views • 24 slides

Consideration on TSN Capabilities and XR Applications in Wi-Fi

This contribution evaluates XR applications in Wi-Fi, focusing on high throughput, low latency, and reliability. It discusses in-car XR entertainment/navigation as an entry-level TSN application and proposes integrating Wi-Fi technologies like 11be for improved performance. The document highlights t

0 views • 17 slides

Achieving Bounded Latency in Data Centers: A Comprehensive Study

Data centers face challenges in providing consistent low latencies due to in-network interference and varying workloads. This study explores solutions to guarantee strong latency performance, mitigate latency variance, and minimize performance degradation for latency-sensitive applications. By analy

0 views • 18 slides

Insight into Tuning Check and Parameter Reconstruction Process

Delve into the process of tuning check and parameter reconstruction through a series of informative images depicting old tuning parameters and data sets. Explore how 18 data and 18 MC as well as 18 MC and 12 MC old tuning parameters play a crucial role in optimizing performance and accuracy. Gain va

0 views • 4 slides

Ultra-Reliable PHY Elements: Optimized Building Blocks for Low Latency and Efficiency

The document presents a deep dive into ultra-reliable PHY elements, focusing on achieving low latency, reduced collision, and energy efficiency. It proposes optimized universal building blocks to address these goals effectively, especially in scenarios where many devices may not receive transmission

0 views • 17 slides

Stronger Semantics for Low-Latency Geo-Replicated Storage

Discusses the importance of strong consistency and low latency in geo-replicated storage systems for improving user experience and revenue. Various storage dimensions, sharding techniques, and consistency models like Causal+ are explored. The Eiger system is highlighted for ensuring low latency by k

0 views • 24 slides

Understanding Latency Variation in Modern DRAM Chips

This research delves into the complexities of latency variation in modern DRAM chips, highlighting factors such as imperfect manufacturing processes and high standard latencies chosen to boost yield. The study aims to characterize latency variation, optimize DRAM performance, and develop mechanisms

0 views • 37 slides

Latency Measurement in IEEE 802.11 for Low Latency Applications

IEEE 802.11-20/0484r0 discusses the importance of latency measurement for low latency applications in WLAN technologies. The document emphasizes the need for improved worst-case latency and jitter, addressing interference issues to ensure guaranteed latency for scheduled transmissions. Various contr

0 views • 13 slides

Understanding Latency in JESD204B Links

Latency in a JESD204B link refers to the time it takes for a signal to travel from input to output, influenced by factors like system setup, device dependencies, clock propagation delays, and signal alignment. Definitions such as Sample-to-Serial Out (S2SO), Link Delay, and Link Latency are crucial

0 views • 46 slides

Multi-AP Preemption for Low-Latency Traffic in IEEE 802.11 Networks

Discussion on the necessity of Multi-AP preemption for low-latency traffic in IEEE 802.11 networks. Addresses issues related to latency-sensitive traffic in overlapping basic service sets (OBSS). Proposes a general solution to enable OBSS APs to transmit urgent low-latency traffic without significan

0 views • 9 slides

New Queue Mechanism for Real-Time Application Considerations in July 2019

In July 2019, considerations were made for a new queue mechanism for real-time applications. The focus was on improving worst-case latency and jitter for latency-critical traffic, such as in online mobile gaming and manufacturing control. The proposed design aims to link access delay directly to req

0 views • 9 slides

Multi-AP Coordination for Low Latency Traffic Transmission

The document discusses the integration of multi-access point (AP) coordination to enhance the transmission of low-latency traffic in wireless networks. It addresses the challenges and introduces modes of operation capable of reducing latency and improving reliability for low-latency (LL) traffic tra

0 views • 9 slides

Coordinated Medium Access for Multi-AP Deployments in IEEE 802.11 Networks

The document discusses a solution to reduce latency, increase throughput, and improve reliability in networks with latency-sensitive traffic by introducing coordination between access points (APs). This involves leveraging mechanisms like Restricted TWT (rTWT) and Coordinated rTWT (C-rTWT) to facili

0 views • 12 slides

PCIe Latency and Performance Test on LX2160A

This document discusses PCIe latency and performance testing using Lmbench and DPDK qdma_demo on LX2160A hardware. It covers test configurations, latency measurements, throughput analysis, and peer-to-peer communication details.

0 views • 12 slides

Low Latency Multi-viewpoint 360 Interactive Video System with Deep Reinforcement Learning

This research focuses on addressing the challenges of achieving low latency and high quality in multi-viewpoint (MVP) 360 interactive videos. The proposed iView system utilizes multimodal learning and a Deep Reinforcement Learning (DRL) module to optimize tile selection, aiming to reduce latency and

0 views • 17 slides

Overlapped Indication for Event-Based Low Latency Traffic Support in IEEE 802.11

The document discusses the importance of reducing latency in Ultra High Rate (UHR) PAR and Event Based Low Latency (LL) traffic support in IEEE 802.11 networks. It introduces the concept of preemption to enhance LL traffic handling and proposes an overlapped LL indication frame to address challenges

0 views • 13 slides