Enhancing Student Success through Block Scheduling at KSU

National Institute for Student Success (NISS) diagnostic analysis at KSU shows the importance of block scheduling in increasing graduation rates and student engagement. Actions to increase registration for full-time schedules and improve student success are underway. The goals of KSU's block schedul

0 views • 10 slides

Understanding Linux Process Scheduling and Priorities

Delve into the intricacies of process scheduling in Linux systems, covering topics such as task prioritization, process states, scheduler decisions, and important scheduling scenarios. Learn about traditional scheduling concerns like throughput and latency, as well as different types of workloads su

1 views • 19 slides

Understanding Irrigation Scheduling for Optimal Crop Yield

Scientific irrigation scheduling plays a vital role in determining the correct timing and quantity of water application for crops to enhance yields efficiently while preserving soil quality. Various criteria are utilized in irrigation scheduling, such as potential evapotranspiration (PET) estimation

12 views • 58 slides

Network Function Abstraction A delicate question of (CPU) affinity?

Exploring the delicate balance of CPU affinity in network function abstraction, including challenges, benefits, and solutions like CPU pinning for network workloads. Learn about the impact on performance and scalability, as well as the importance of proper configuration in virtual and physical envir

3 views • 40 slides

Enhanced Scheduling Method for Low Latency Traffic in IEEE 802.11-24/0091r1

This document presents an enhanced scheduling method for handling low latency traffic in IEEE 802.11 networks. It focuses on supporting deterministic and event-based latency-sensitive traffic, addressing challenges in scheduling and resource allocation. The proposed method aims to improve the reliab

8 views • 12 slides

Understanding Computer Architecture: CPU Structure and Function

Delve into the intricate world of computer architecture with Prof. Dr. Nizamettin AYDIN as your guide. Explore topics such as CPU structure, registers, instruction cycles, data flow, pipelining, and handling conditional branches. Gain insights into the responsibilities of a CPU, internal structures,

0 views • 39 slides

Understanding Scheduling Terminology and Concepts in MyEdBC

Explore the key terminology and concepts related to scheduling in MyEdBC, including the Build view, scenarios, flat and rotated schedules, patterns, and base terms. Get insights into setting up scheduling structures and preferences, as well as managing course requests and staff information. Enhance

1 views • 13 slides

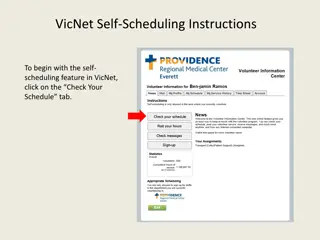

VicNet Self-Scheduling Instructions

Begin using the self-scheduling feature in VicNet by following step-by-step instructions, such as checking available shifts, selecting a day to volunteer, viewing specific times, scheduling yourself, and managing your shifts. Contact Volunteer Services for additional help or questions.

1 views • 6 slides

GPU Scheduling Strategies: Maximizing Performance with Cache-Conscious Wavefront Scheduling

Explore GPU scheduling strategies including Loose Round Robin (LRR) for maximizing performance by efficiently managing warps, Cache-Conscious Wavefront Scheduling for improved cache utilization, and Greedy-then-oldest (GTO) scheduling to enhance cache locality. Learn how these techniques optimize GP

0 views • 21 slides

Time-Aware Scheduling Capabilities in IEEE 802.11be

Describing necessary enhancements to enable Time-Aware Scheduling in IEEE 802.11be for time-sensitive applications. The focus is on aligning with the 802.1Qbv standard to address latency, jitter, and reliability issues, presenting a structured outline of requirements and configurations essential for

0 views • 24 slides

Understanding Scheduling Algorithms in Operating Systems

Exploring the world of scheduling in operating systems, this content covers various aspects such as introduction to scheduling, process behavior, bursts of CPU usage, CPU-bound and I/O-bound processes, when to schedule processes, and the differences between non-preemptive and preemptive scheduling a

0 views • 34 slides

Understanding CPU Scheduling in Operating Systems

In a single-processor system, processes take turns running on the CPU. The goal of multiprogramming is to keep the CPU busy at all times. CPU scheduling relies on the alternating CPU and I/O burst cycles of processes. The CPU scheduler selects processes from the ready queue to execute when the CPU i

0 views • 26 slides

Greedy Method for Task Scheduling Problems

The greedy method is a powerful algorithm design technique used in solving various optimization problems. In the context of task scheduling, we explore two specific problems: minimizing the number of machines needed to complete all tasks and maximizing the number of non-overlapping intervals on a si

1 views • 58 slides

Improving GPGPU Performance with Cooperative Thread Array Scheduling Techniques

Limited DRAM bandwidth poses a critical bottleneck in GPU performance, necessitating a comprehensive scheduling policy to reduce cache miss rates, enhance DRAM bandwidth, and improve latency hiding for GPUs. The CTA-aware scheduling techniques presented address these challenges by optimizing resourc

0 views • 33 slides

Simplifying Residency Shift Scheduling with Mathematical Programming Techniques

This project, led by Professor Amy Cohn and William Pozehl, aims to demonstrate how mathematical programming techniques can simplify the complex task of residency shift scheduling. The Residency Shift Scheduling Game highlights the challenges of manual scheduling and the ease of using mathematical p

1 views • 37 slides

Understanding Disk Scheduling in Multiprogramming Systems

In a multiprogramming system, several processes may contend for disk resources. Disk scheduling aims to efficiently share the disk drive's resources among processes, maximizing I/O request satisfaction while minimizing head movement. Various disk scheduling policies like FCFS, SSTF, and SCAN aim to

1 views • 22 slides

Understanding Operating System Scheduling Principles

Operating system scheduling involves making decisions on resource allocation among multiple clients, determining who gets to use the resource next and for how long. Different scheduling algorithms aim to achieve specific goals, such as maximizing throughput, minimizing waiting time, ensuring fairnes

0 views • 57 slides

Orchestrated Scheduling and Prefetching for GPGPUs

This paper discusses the implementation of an orchestrated scheduling and prefetching mechanism for GPGPUs to enhance system performance by improving IPC and overall warp scheduling policies. It presents a prefetch-aware warp scheduler proposal aiming to make a simple prefetcher more capable, result

0 views • 46 slides

Evolution of Shift Work Scheduling at an Accelerator Facility

Operators at an accelerator facility used to rely on manual processes and multiple systems for shift work scheduling and timesheet management. With the implementation of new interactive applications, the process has been streamlined, allowing for better planning, efficient submission of timesheets,

0 views • 32 slides

Efficient Department Scheduling for Timetabling Success

Efficient timetabling for a department involves various stages like data entry, draft timetable creation, feedback collection, production of the final timetable, schedule adjustments, and publication. Key information needed includes faculty availability, room inventory, specific scheduling parameter

0 views • 59 slides

Multiserver Stochastic Scheduling Analysis

This presentation delves into the analysis and optimality of multiserver stochastic scheduling, focusing on the theory of large-scale computing systems, queueing theory, and prior work on single-server and multiserver scheduling. It explores optimizing response time and resource efficiency in modern

0 views • 38 slides

Effective UCOR Course Scheduling Strategies

This resource provides specific instructions, tips, and reminders for scheduling UCOR courses in CLSS. Learn about approved titles, using the CLSS heat map, cross-listing steps, workflow tips, deadlines, and more. Access CLSS and UCOR resources, including training materials, production calendars, an

0 views • 13 slides

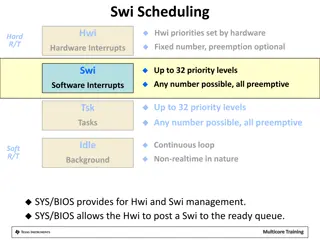

Real-Time Interrupt Handling and Scheduling in SYS/BIOS

This content covers the management of hardware and software interrupts, interrupt priorities, scheduling rules, and execution flow for real-time systems using SYS/BIOS. It discusses the handling of interrupts by the Hardware Interrupt (Hwi) and Software Interrupt (Swi) components, priority levels, p

0 views • 4 slides

New Scheduling Policy: ServerFilling-SRPT in Multiserver Job Model

Discusses a new scheduling policy, ServerFilling-SRPT, designed to favor small jobs in the multiserver job model. The policy aims to minimize mean response time by prioritizing jobs with the least remaining size order and arranging them based on server needs. The approach involves finding minimal su

0 views • 16 slides

Understanding Scheduling in Operating Systems: A Comprehensive Overview

This content delves into the intricate details of scheduling in operating systems, covering the goals, various scheduling algorithms, multiprogramming concepts, decision-making processes for resource allocation, timing considerations, scheduling objectives, and performance criteria such as throughpu

0 views • 42 slides

Comprehensive Guide to Virtualization Infrastructure Administration

Explore the world of virtualization infrastructure administration, covering resources such as CPU, memory, storage, and network I/O. Learn about resource management, CPU scheduling, memory efficiency, and virtual memory management in virtualized environments. Dive into topics like vCPU mapping, prop

0 views • 10 slides

College of Medicine M4 Scheduling Information for Class of 2021

Important scheduling timeline information for 4th-year medical students at the College of Medicine. Key dates include deadlines for hardship requests, core clerkship preferences, Geriatrics/Palliative Medicine enrollment, scheduling rounds, and publication rules. Compliance with specific requirement

0 views • 8 slides

Improving Job Scheduling with Nudge Policy

Explore the innovative Nudge policy for stochastic improvement upon First-Come-First-Served (FCFS) scheduling. The Nudge policy introduces a new approach with better performance tradeoffs compared to traditional scheduling methods. Discover how Nudge outperforms FCFS across various job size distribu

0 views • 21 slides

Job Scheduling Across Geo-distributed Datacenters

Scheduling jobs across geo-distributed datacenters poses challenges such as optimizing job completion time, reducing data transfer costs, and coordinating tasks across multiple locations. Various strategies like reordering-based approaches and scheduling heuristics are explored to enhance job schedu

0 views • 32 slides

Insights into Volunteer Scheduling and Management

Exploring the intricacies of volunteer scheduling, this informative guide covers topics such as creating schedule slots, weighing the pros and cons of scheduling, opportunity scheduling, monthly calendars, slot summaries, volunteer and opportunity listings, and more. Dive into the world of volunteer

0 views • 21 slides

Understanding CPU Structure and Function in Computer Organization and Architecture

Exploring the intricate details of CPU architecture, this content delves into the essential tasks of fetching, interpreting, processing, and writing data. It discusses the significance of registers, user-visible registers, general-purpose registers, and condition code registers in CPU operations. Ad

0 views • 83 slides

Understanding CPU Architecture in Computing for GCSE Students

Explore the fundamental concepts of CPU architecture, including the Von Neumann Architecture, common CPU components like ALU and CU, and how characteristics such as Clock Speed and Cache Size impact performance. Learn about the Fetch-Execute Cycle and the essential hardware components of a computer

0 views • 18 slides

Intel CPU Architectures Overview: Evolution and Features

Explore the evolution and key features of various Intel CPU architectures including Pentium, Core, and Pentium 4 series. Learn about the pipeline stages, instruction issue capabilities, branch prediction mechanisms, cache designs, and memory speculation techniques employed in these processors. Gain

0 views • 11 slides

Understanding the Basics of Multi-Stage Architecture in CPU Design

The article explains the fundamentals of a multi-stage digital processing system in computer organization, focusing on the central processing unit (CPU). It covers topics such as instruction execution, processor building blocks, and the benefits of pipelined operation. Concepts like fetching, decodi

0 views • 42 slides

University Space Scheduling Guidelines

University space scheduling guidelines prioritize academic courses and campus use, emphasizing the need for more available space. The policy outlines expectations, scheduling guidelines, and the management of laboratory and studio spaces. It also addresses the direct scheduling of such spaces for sp

0 views • 14 slides

Understanding Operating System Concepts: Multiprogramming, Multiprocessing, Multitasking, and Multithreading

In the realm of operating systems, terms like multiprogramming, multiprocessing, multitasking, and multithreading can often be confusing due to their similar appearance but distinct meanings. These concepts play a crucial role in efficiently managing resources in a computing system, particularly in

0 views • 6 slides

Understanding CPU Scheduling Concepts at Eshan College of Engineering, Mathura

Dive into the world of CPU scheduling at Eshan College of Engineering in Mathura with Associate Professor Vyom Kulshreshtha. Explore topics such as CPU utilization, I/O burst cycles, CPU burst distribution, and more. Learn about the CPU scheduler, dispatcher module, scheduling criteria, and the impl

0 views • 18 slides

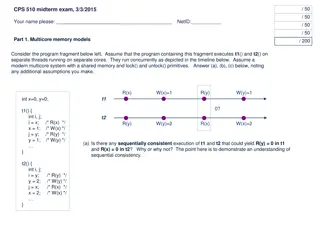

Multicore Memory Models and CPU Protection in Operating Systems

This content covers topics related to multicore memory models, synchronization, CPU protection levels in Dune-enabled Linux systems, and concurrency control in multithreaded programs. The material includes scenarios, questions, and diagrams to test understanding of these concepts in the context of t

0 views • 10 slides

Overview of Project Scheduling in Engineering Management

The lecture covers planning and scheduling in engineering management, focusing on activity and event scheduling techniques, bar charts, critical path analysis, and addressing project scheduling principles. It discusses the objectives of the lecture, the difference between planning and scheduling, th

0 views • 29 slides

Understanding Barrel Shifter in CPU Design

Barrel shifter is a vital component in CPU architecture, enabling shifting and rotating operations on data inputs based on control signals. The shifter consists of two main blocks - Shift-and-Rotate Array (SARA) and Control Logic. SARA, designed with multiple stages of cells, executes shift and rota

0 views • 12 slides