SEAL: Scalable Memory Fabric for Silicon Interposer-Based Systems

SEAL lab focuses on designing a scalable hybrid memory fabric for silicon interposer-based multi-core systems to support memory-intensive applications like in-memory computing. The lab's research aims to provide low-latency, high-bandwidth processor-memory communication through innovative topology,

0 views • 27 slides

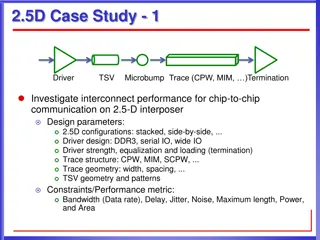

Investigating Chip-to-Chip Communication Performance on 2.5D Interposer

Investigate the performance of chip-to-chip communication on a 2.5D interposer by analyzing interconnect parameters such as configurations, driver design, trace structure, TSV geometry, and channel modeling. Explore methods like SPICE simulation and MATLAB GUI for performance estimation and optimiza

0 views • 18 slides