Advanced Controls and Systems Development in Accelerator Technology

Explore the cutting-edge technologies and extensive experience in system development within the Accelerator Control Division at BARC. The workshop covers a range of topics including SoC-FPGA system architecture, GUI development for RF control, EPICS application development, and lessons learned in implementing real-time control systems. Discover the significance of SoC-FPGA integration, application languages expertise, and key takeaways for system architecture advancement.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

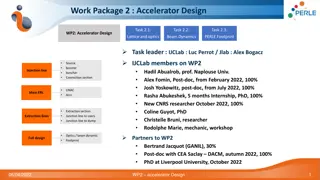

PIP-II Technical Workshop Controls Round Table Sandeep Bharade, Radhika Nasery Accelerator Control Division, BARC

INDEX Controls Experience Application Languages and Framework Lessons Learned SoC-FPGA System Architecture CSS GUI for LLRF CSS GUI for RF-Protection and Interlock Eclipse Plug-in Development Eclipse State Based Plug-in Eclipse IOC Database Configuration Plug-in EPICS ASYN IOC Plug-in Looking Forward To

Controls Experience: Technologies and Systems Development Experience: On custom Frond End state-based architecture for various subsystem development. We have subsystems based on Heterogeneous hardware platforms like cPCI VME SoC Standard software architecture for subsystem development and seamless interface by: MODBUS/TCP bridge Cross-compiled EPICS IOC Legacy systems were developed on cPCI architecture using MODBUS/TCP and EPICS server Low Level RF Programmable Timing Control,

Controls Experience: Application Languages and Framework Experience with the following: Software Python, PyEPICS C C++ Java Firmware VHDL Verilog GUI EPICS Qt CSS

Lessons Learned LLRF control system under IIFC collaboration has been developed on a network connected SoC-FPGA The on chip bridge between the ARM HPS processor and FPGA offers high throughput DAQ. Linux based EPICS IOC has been developed with FPGA device support for control and DAQ of LLRF. Linux has network bottlenecks which limit the performance. To address this issue RTEMS-5 + EPICS-7 has been ported to Cyclone-V based SoC-FPGA. Benchmarking of the real time EPICS IOC is under progress. To cater to future requirements, RTEMS Arria-10 BSP layer has been developed. Efforts are on to port network device drivers.

Takeaway for system architecture: SoC-FPGA SoC FPGA HPS GUI EPICS IOC APPLICATIONS DEVICE DRIVER LINUX KERNEL DUAL CORE ARM PROCESSOR h2sdra m _bridge interrupt h2f_bridge h2f_bridge SDRAM mSGDMA FPGA REGISTERS APPLICATION LOGIC ON CHIP RAM 6

Takeaway for system architecture: CSS LLRF GUI

Takeaway for system architecture: CSS GUI for RF-Protection and Interlock

Lessons in framework development: Eclipse State Based Plug-in Eclipse is a widely used open source and common IDE platform for computer programming. It contains a base workspace and extension points for connecting plug-ins and customizing the environment. A plug-in is used to group the code into a modular, extendable and sharable unit to enhance functionality of the IDE. Eclipse plug-in are developed for EPICS State Machine based editor EPICS database configuration plugin EPICS device support 9

Lessons in framework development: Eclipse State Based Plug-in EPICS uses state notation language for state machine based. Editor plug-in has been developed which will assist in Prompting expected keywords and parameters during editing Minimal check for conformance with the grammar. For this State notation language grammar has been written in JAVACC Parser and abstract syntax tree are generated Editor plug-in has been implemented 10

Lessons in framework development: Eclipse State Based Plug-in 11

Lessons in framework development: Eclipse IOC Database Configuration Plug-in 12

Lessons in framework development: EPICS ASYN IOC Plug-in Asyn device support is a EPICS facility for interfacing device specific code to low level communication drivers. SoC HPS HPS Asyn device support is implemented for Database development using asynRecord Interfacing device driver to IOC using sysfs Interrupt services and callback routines Register interface to access the memory mapped registers on FPGA EPICS INPUT OUTPUT CONTROLLER DEVICE DRIVER LINUX KERNEL DUAL CORE ARM PROCESSOR

Lessons in framework development: EPICS ASYN IOC Plug-in SoC HPS HPS EPICS INPUT OUTPUT CONTROLLER DEVICE DRIVER LINUX KERNEL DUAL CORE ARM PROCESSOR 14

Looking Forward To DPDK Framework EPICS IOC interface with DPDK Performance evaluation parameters and procedure of EPICS IOC Time-stamping of LLRF EPICS IOC PV EPICS-3 to EPICS-7 database(dB) migration procedure Centralised database vs local database management Evolution of uTCA as a common platform Development of Machine Learning algorithms and their integration in the accelerator control system framework