Vector Processing Definitions

A vector in computing is an ordered set of scalar data items, processed efficiently by vector processors using hardware components like vector registers and functional pipelines. Learn about vectorization, vector stride, and various types of vector instructions for faster and more efficient data processing.

Uploaded on Feb 17, 2025 | 0 Views

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

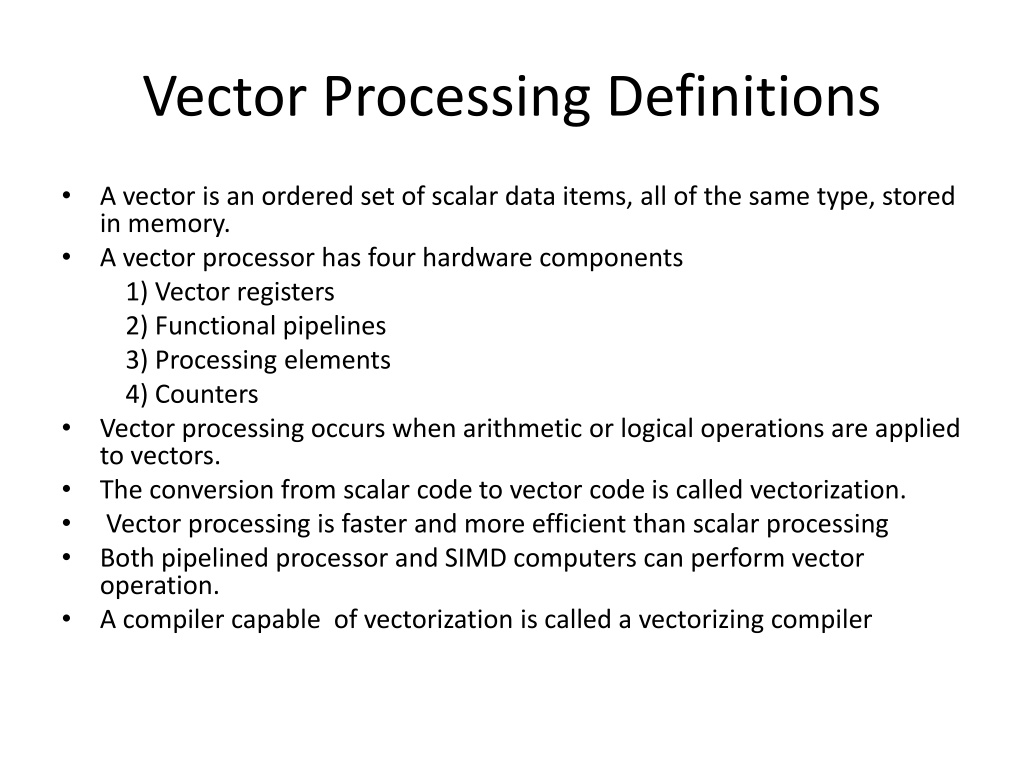

Vector Processing Definitions A vector is an ordered set of scalar data items, all of the same type, stored in memory. A vector processor has four hardware components 1) Vector registers 2) Functional pipelines 3) Processing elements 4) Counters Vector processing occurs when arithmetic or logical operations are applied to vectors. The conversion from scalar code to vector code is called vectorization. Vector processing is faster and more efficient than scalar processing Both pipelined processor and SIMD computers can perform vector operation. A compiler capable of vectorization is called a vectorizing compiler

Vector stride The fixed addressing increment between two successive vector elements called stride. Assume a n m matrix where n and m are the no. of rows and column respectively. Each element is stored in one memory location. Accessing the matrix in row major order the stride is one. Accessing the matrix in column major order the stride is m. Accessing the matrix in diagonally the stride is m+1 if it is a square matrix (row and column size are same).

Example of vector stride m a11 a12 a1m a21 a22 a2m n .. .. .. .. an1 an2 anm n m matrix When the matrix is accessed in row major order then elements are accessed according to a11, a12, a13, ..a1m . Here stride is 1 because of the fixed address increment of two successive elements is 1. When the matrix is accessed in column major order then elements are accessed according to a11, a21, a31, ..an1 . Here stride is m because of the fixed address increment of two successive elements is m. When the matrix is accessed in diagonally (only if possible when rows and columns are same) then elements are accessed according to a11, a22, a33, ..anm . Here stride is m+1 because of the fixed address increment of two successive elements is m+1.

Vector Instruction Types 1) Vector-vector instructions f1: Vi Vj Where operation over one vector register produce results in another vector register. Example: V1 = sin(V2) f2: Vj Vk Vi Where operation over two vector registers produce results in another vector register. Example: V3 = V1 + V2 Vj Register Vk Register Vi Register Click here n 1 2 Functional unit Vector-vector instruction Click here

Vector Instruction Types contd. 2) Vector-scalar instructions f3: s Vi Vj Where operation over one vector register and a scalar produce results in another vector register. Example: s * V1 = V2 Vi Register Vj Register s Register n 1 2 Functional unit Click here Vector-scalar instruction 3) Vector-memory instructions f4: M V Vector Load f5: V M Vector Store Load the vector data from memory to vector register is called vector load. Store the vector data from vector register to memory is called vector store. Memory path ( Vector Load ) Vi Register Memory Memory path ( Vector Store ) Vector-memory instruction

Vector Instruction Types contd. 4) Vector reduction instructions Here after vector operation over single or multiple vector produce a scalar value. f6: Vi s Example : s= max(V1) Similarly it can be included finding the minimum, sum and mean value of all elements in a vector. f7: Vi Vj s Example : s = ?=1 ?? ?? Click here ?

Vector Instruction Types contd. 5) Gather and scatter instructions These instructions use two vector registers to gather or to scatter vector elements randomly through out the memory. f8: M Vi Vj Gather Example: M V0 V1 The gather instruction is the mapping operation of memory to vector registers. Here VL register indicates the length of V0 and V1 registers( length=4). A0 is the base register that holds the base address. V0 is used as a index register. Every time the content of V0 will be added with A0 and generate the memory addresses. The first location of V0 register is 4. So the content of 104 (100+4) memory address (600) will be stored into first location of V1. The gather instruction transfers the contents (600, 400, 250, 200) of non-sequential memory locations (104, 102,107,100) to four elements of a vector register V1. V0 Register V1 Register Contents Address 100 101 102 103 104 105 106 107 108 600 400 250 200 200 4 2 7 0 300 400 500 600 700 100 250 350 VL Register A0 4 100 Memory Gather Instruction

Vector Instruction Types contd. f9: Vi Vj M Scatter Example: V0 V1 M The scatter instruction reverses the mapping operation. Here VL register indicates the length of V0 and V1 registers( length=4). A0 is the base register that holds the base address. V0 is used as a index register. Every time the content of V0 will be added with A0 and generate the memory addresses. The first location of V0 register is 4. So the content of 104 (100+4) memory address must be 200 (first location of V1). Similarly next data will be stored into memory. V0 Register V1 Register Contents Address 200 300 400 500 500 100 101 102 103 104 105 106 107 108 4 2 7 0 300 200 400 VLRegister A0 4 100 Memory Scatter Instruction

Vector Instruction Types contd. 6) Masking instructions f10: Vi Vm Vj Example: V0 Vm V1 The masking instruction is used for compressing a long vector into a short index vector. The masking instruction is very useful in handling sparse matrices. Sparse matrices are those in which most of the elements are zero. The contents of vector register V0 are tested for zero and nonzero elements. A masking register Vm is used to store the test result. After testing and forming the masking vector in Vm, the corresponding nonzero indices are stored in the V1 register. The VL register indicates the length of vector being tested. V1 Register V0 Register 01 03 04 07 08 0 -1 0 5 -15 VL Register 9 0 0 010110011 24 -7 Vm Register Masking Instruction In V0 register indices are started from 0 and ended with 8.

Back V1 V2 Example: V1 = sin(V2) 0.5 30 After applying sin operation over V2 0.707 45 0.866 60 1 90 V1 V2 V3 10 20 30 After addition operation of V1 and V2 5 15 20 Example: V3 = V1 + V2 20 10 30 15 30 45

Back Example: s * V1 = V2 V1 V2 s 30 60 After multiplication of V1 and s 2 15 30 20 40 40 80

Back Example : s = max(V1) V1 30 After finding the maximum of V1 15 s 40 20 40