Understanding Interconnection Networks in Multiprocessor Systems

Interconnection networks are essential in multiprocessor systems, linking processing elements, memory modules, and I/O units. They enable data exchange between processors and memory units, determining system performance. Fully connected interconnection networks offer high reliability but require extensive cabling due to numerous connections. These networks play a crucial role in parallel processing by routing data efficiently. Explore how interconnection networks function and their significance in enhancing multiprocessor system performance.

- Interconnection Networks

- Multiprocessor Systems

- Parallel Processing

- Fully Connected Topology

- System Performance

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

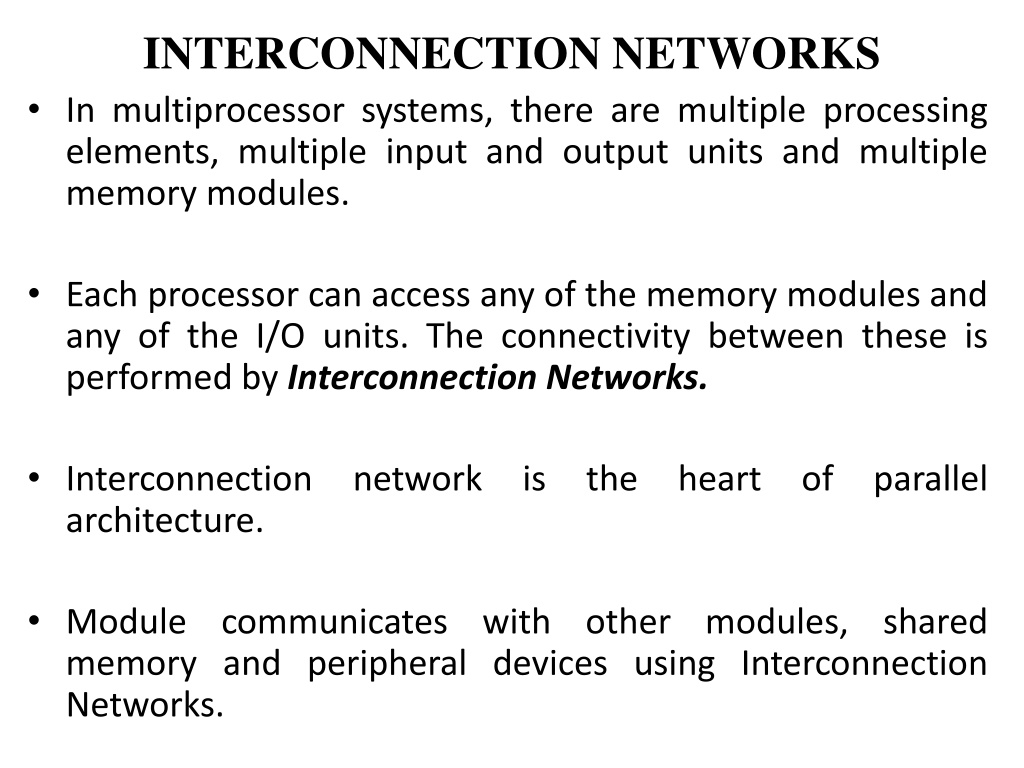

INTERCONNECTION NETWORKS In multiprocessor systems, there are multiple processing elements, multiple input and output units and multiple memory modules. Each processor can access any of the memory modules and any of the I/O units. The connectivity between these is performed by Interconnection Networks. Interconnection architecture. network is the heart of parallel Module communicates with other modules, shared memory and peripheral devices using Interconnection Networks.

An exchanging data between two processors in a multistage network. Interconnection Network is used for The multiprocessor has one global shared memory and each processor has a small local memory. Note: Multistage network is a class of high-speed computer networks processing elements(PEs) on one end of the network and memory elements(MEs) on the other end connected by switching elements (SEs). usually composed of

The processor can access data from memory associated with another processor or from shared memory using Interconnection network. Thus, it plays a central role in determining the overall performance of multiprocessor systems. It involves logical connection that is, what nodes can be considered as neighbors for the purpose of sending and receiving messages. It is needed in parallel processing because, when more than one processor needs to access a memory structure, Interconnection networks are needed to route data.

Interconnection networks are like customary network systems consisting of nodes and edges. The nodes are switches with few inputs and few outputs (say n-input and m-output) lines. Depending upon the switch connection, the data is forwarded from input lines to output lines. The interconnection network is placed between various devices in the multiprocessor network. From processors to memories (concurrent access to a shared memory structure) or from one PE (processor + memory) to another to provide a message-passing facility.

Fully Connected Interconnection Network Fully connected: This is the most powerful interconnection topology. In this each node is directly connected to all other nodes. The shortcoming of this network is that it requires too many connections. In graph theory, it is known as complete graph Characterized by high degree of reliability due to multiple paths for data that are provided by the large number of redundant links between nodes.

A fault in one terminal on the network will not affect the rest as data has multiple redundancy paths. However large amount of cabling is required, i.e the number of connections grows quadratically with the number of nodes. A fully connected topology is mostly seen in military applications

Linear Array Linear Array: this is a most fundamental Interconnection pattern. In this, processors are connected in a linear one-dimensional array. The first and last processors are connected with one adjacent processor processing elements are connected with two adjacent processors. and the middle It is a one-dimensional Interconnection Network.

Linear Array PE1 PE2 PE3 PEn

Mesh Interconnection Mesh Interconnection: is a two dimensional network. In this all processing elements are arranged in a two dimensional grid. The processor in rows i and column j are denoted by PEi. The processors at the corner can communicate with two nearest neighbors i.e. PE00 can communicate with PE01 and PE10. The processor at the boundary can communicate with 3 adjacent processing elements i.e. PE01 can communicate with PE00, PE02 and PE11 while internally placed processors can communicate with 4 adjacent processors i.e. PE11 can communicate with PE01, PE10, PE12, and PE21. It suffers from congestion at its center.

Systolic Array Systolic Array: This interconnection network is a type of pipelined array architecture and it is designed for multidimensional flow of data. It is used for implementing fixed algorithms. Systolic array designed for performing matrix multiplication is shown below. All interior nodes have degree 6. Note: a pipeline is a set of data elements, through which computer architecture allows the next instruction to be fetched while the processor is performing.

Note: a pipeline is a continuous and somewhat overlapped movement of instruction to the processor or it is the arithmetic steps taken by the processor to perform an instruction. With pipelining, computer architecture allows the next instructions be fetched while the processor is performing arithmetic operations holding them in a buffer close to the processor until each instruction operation can be performed. Without pipelining, a computer processor gets the first instruction from memory, performs the operation it calls for and then get the next instruction from memory and so on and so forth

Ring Interconnection Ring Interconnection: This is a simple linear array where the end nodes are connected. It is equivalent to a mesh with wrap around connections. In this connection, data can be moved from any processor to any other by a sequence of cyclic shifts. The data transfer in a ring is normally one direction.

Tree Interconnection Tree Interconnection: In the tree interconnection network, processors are arranged in a complete binary tree pattern.

Assignments With the aid of diagrams, briefly explain the following interconnection networks: The Crossbar Network Cube Interconnection Network Fat Tree Connection