Configuring 8MHz Bus with 8MHz Crystal for PEE Mode

Configuring a system with an 8MHz bus using an 8MHz crystal for PEE (PLL Engaged External) mode involves a series of steps such as setting register values, waiting for specific conditions to be met, selecting clock sources, and ensuring PLL stability. The detailed configuration process ensures proper initialization, crystal usage, clock selection, and PLL locking for efficient operation.

Uploaded on Sep 24, 2024 | 0 Views

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

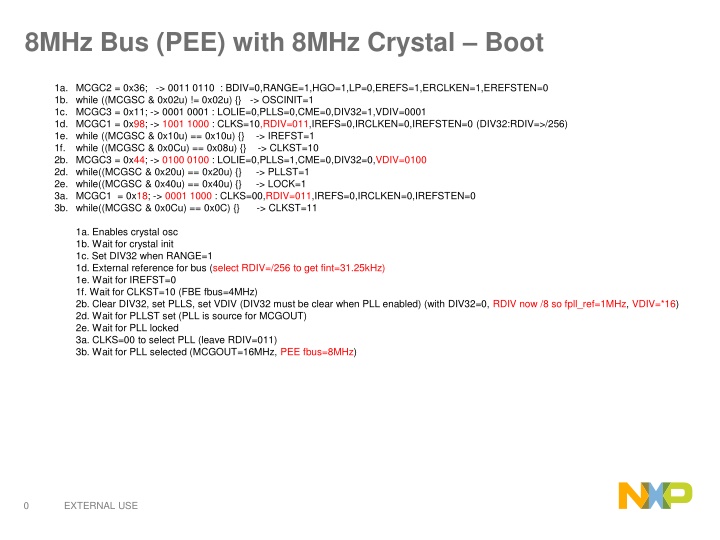

8MHz Bus (PEE) with 8MHz Crystal Boot 1a. 1b. 1c. 1d. 1e. 1f. 2b. 2d. 2e. 3a. 3b. MCGC2 = 0x36; -> 0011 0110 : BDIV=0,RANGE=1,HGO=1,LP=0,EREFS=1,ERCLKEN=1,EREFSTEN=0 while ((MCGSC & 0x02u) != 0x02u) {} -> OSCINIT=1 MCGC3 = 0x11; -> 0001 0001 : LOLIE=0,PLLS=0,CME=0,DIV32=1,VDIV=0001 MCGC1 = 0x98; -> 1001 1000 : CLKS=10,RDIV=011,IREFS=0,IRCLKEN=0,IREFSTEN=0 (DIV32:RDIV=>/256) while ((MCGSC & 0x10u) == 0x10u) {} -> IREFST=1 while ((MCGSC & 0x0Cu) == 0x08u) {} -> CLKST=10 MCGC3 = 0x44; -> 0100 0100 : LOLIE=0,PLLS=1,CME=0,DIV32=0,VDIV=0100 while((MCGSC & 0x20u) == 0x20u) {} -> PLLST=1 while((MCGSC & 0x40u) == 0x40u) {} -> LOCK=1 MCGC1 = 0x18; -> 0001 1000 : CLKS=00,RDIV=011,IREFS=0,IRCLKEN=0,IREFSTEN=0 while((MCGSC & 0x0Cu) == 0x0C) {} -> CLKST=11 1a. Enables crystal osc 1b. Wait for crystal init 1c. Set DIV32 when RANGE=1 1d. External reference for bus (select RDIV=/256 to get fint=31.25kHz) 1e. Wait for IREFST=0 1f. Wait for CLKST=10 (FBE fbus=4MHz) 2b. Clear DIV32, set PLLS, set VDIV (DIV32 must be clear when PLL enabled) (with DIV32=0, RDIV now /8 so fpll_ref=1MHz, VDIV=*16) 2d. Wait for PLLST set (PLL is source for MCGOUT) 2e. Wait for PLL locked 3a. CLKS=00 to select PLL (leave RDIV=011) 3b. Wait for PLL selected (MCGOUT=16MHz, PEE fbus=8MHz) EXTERNAL USE 0

8MHz Bus (PEE) with 8MHz Crystal Application MCGTRM = 0xFFAF; MCGSC = 0xFFAE; MCGC2 = 0x36; /* MCGC2: BDIV=0,RANGE=1,HGO=1,LP=0,EREFS=1,ERCLKEN=1,EREFSTEN=0 */ While (!MCGSC_OSCINIT) {} // wait until external reference is stable MCGC3 |= 0x10; /* MCGC3: DIV32=1 */ MCGC1 = 0x98; /* MCGC1: CLKS=2,RDIV=3,IREFS=0,IRCLKEN=0,IREFSTEN=0 */ While (MCGSC_IREFST) {} // wait until external reference is selected While ((MGCSC & 0x0C) != 0x08) {} // wait until external clock is selected as a bus clock reference MCGC2 = 0x3E; /* MCGC2: BDIV=0,RANGE=1,HGO=1,LP=1,EREFS=1,ERCLKEN=1,EREFSTEN=0 */ MCGC3 = 0x44; /* MCGC3: LOLIE=0,PLLS=1,CME=0,DIV32=0,VDIV=4 */ MCGC2 &= ~0x08; /* MCGC2: LP=0 */ While (!MCGSC_PLLST) {} // wait until PLL is selected While (!MCGSC_LOCK) () // wait until PLL is locked MCGC1 = 0x18; /* MCGC1: CLKS=0,RDIV=3,IREFS=0,IRCLKEN=0,IREFSTEN=0 */ While ((MCGSC & 0x0C) != 0x0C) {} // wait until PLL clock is selected as a bus clock reference /* now in PEE with 8MHz crystal, fpll_ref=1MHz, fbus=8MHz */ 1a. 1b. 1c. 1d. 1e. 1f. 2a. 2b. 2c. 2d. 2e. 3a. 3b. 1a. Enables crystal osc 1b. Wait for crystal init 1c. Set DIV32 when RANGE=1 1d. External reference for bus (select RDIV=/256 to get fint=31.25kHz for FLL even though not used for this operation) 1e. Wait for IREFST=0 1f. Wait for CLKST=10 (FBE fbus=4MHz) 2a. Set LP to disable FLL in FBE 2b. Clear DIV32, set PLLS, set VDIV (DIV32 must be clear when PLL enabled) (with DIV32=0, RDIV now /8 so fpll_ref=1MHz) (VDIV=*16) 2c. Clear LP to enable PLL in PBE 2d. Wait for PLLST set (PLL is source for MCGOUT) 2e. Wait for PLL locked 3a. CLKS=00 to select PLL 3b. Wait for PLL selected (MCGOUT=16MHz, PEE fbus=8MHz) EXTERNAL USE 1

16MHz Bus (PEE) with 8MHz Crystal Application MCGTRM = 0xFFAF; /* Internal oscillator trim */ MCGSC = 0xFFAE; MCGC2 = 0x36; /* MCGC2: BDIV=0,RANGE=1,HGO=1,LP=0,EREFS=1,ERCLKEN=1,EREFSTEN=0 */ While (!MCGSC_OSCINIT) {} // wait until external reference is stable MCGC3 |= 0x10; /* MCGC3: DIV32=1 */ MCGC1 = 0x98; /* MCGC1: CLKS=2,RDIV=3,IREFS=0,IRCLKEN=0,IREFSTEN=0 */ While (MCGSC_IREFST) {} // wait until external reference is selected While ((MGCSC & 0x0C) != 0x08) {} // wait until external clock is selected as a bus clock reference MCGC2 = 0x3E; /* MCGC2: BDIV=0,RANGE=1,HGO=1,LP=1,EREFS=1,ERCLKEN=1,EREFSTEN=0 */ MCGC3 = 0x48; /* MCGC3: LOLIE=0,PLLS=1,CME=0,DIV32=0,VDIV=8 */ MCGC2 &= ~0x08; /* MCGC2: LP=0 */ While (!MCGSC_PLLST) {} // wait until PLL is selected While (!MCGSC_LOCK) () // wait until PLL is locked MCGC1 = 0x18; /* MCGC1: CLKS=0,RDIV=3,IREFS=0,IRCLKEN=0,IREFSTEN=0 */ While ((MCGSC & 0x0C) != 0x0C) {} // wait until PLL clock is selected as a bus clock reference /* now in PEE with 8MHz crystal, fpll_ref=1MHz, fbus=16MHz */ 1a. 1b. 1c. 1d. 1e. 1f. 2a. 2b. 2c. 2d. 2e. 3a. 3b. 1a. Enables crystal osc 1b. Wait for crystal init 1c. Set DIV32 when RANGE=1 1d. External reference for bus (select RDIV=/256 to get fint=31.25kHz for FLL even though not used for this operation) 1e. Wait for IREFST=0 1f. Wait for CLKST=10 (FBE fbus=4MHz) 2a. Set LP to disable FLL in FBE 2b. Clear DIV32, set PLLS, set VDIV (DIV32 must be clear when PLL enabled) (with DIV32=0, RDIV now /8 so fpll_ref=1MHz) (VDIV=*32) 2c. Clear LP to enable PLL in PBE 2d. Wait for PLLST set (PLL is source for MCGOUT) 2e. Wait for PLL locked 3a. CLKS=00 to select PLL 3b. Wait for PLL selected (MCGOUT=32MHz, PEE fbus=16MHz) EXTERNAL USE 2

Step 1a. 1b. 1c. 1d. 1e. 1f. 2a. 2b. 2c. 2d. 2e. 3a. 3b. Boot C2=36 LP=0 OSCINIT=1? C3=11 DIV32=1, VDIV=0001 C1=98 CLKS=10, RDIV=011 IREFST=0? CLKST=10? C2=NA LP=0 C3=44 PLLS=1, DIV32=1, VDIV=0100 C3=44 PLLS=1, DIV32=0, VDIV=0100 C3=48 PLLS=1, DIV32=0, VDIV=1000 C2=NA LP=0 C2=36 LP=0 PLLST=1? PLLST=1? LOCK=1? LOCK=1? C1=18 CLKS=00, RDIV=011 C1=18 CLKS=00, RDIV=011 CLKST=11? CLKST=11? 8MHz crystal, 8MHz bus 8MHz crystal, 8MHz bus (FCDIV=0x27) (FCDIV=0x27) App (8MHz) C2=36 LP=0 OSCINIT=1? C3=11 DIV32=1, VDIV=0001 C1=98 CLKS=10, RDIV=011 IREFST=0? CLKST=10? C2=3E LP=1 App (16MHz) C2=36 LP=0 OSCINIT=1? C3=11 DIV32=1, VDIV=0001 C1=98 CLKS=10, RDIV=011 IREFST=0? CLKST=10? C2=3E LP=1 C2=36 LP=0 PLLST=1? LOCK=1? C1=18 CLKS=00, RDIV=011 CLKST=11? 8MHz crystal, 16MHz bus (FCDIV=0x49) EXTERNAL USE 3