Comparison Analysis of LMK04832 vs LMK0482x

General specifications comparison between LMK04832, LMK04828, LMK04821, and LMK04826 including parameters like VCO frequency range, maximum output frequency, input frequencies, PLL specifications, supply voltage, operating temperature, and output formats. Clock output formats, dividers, and delays detailed for LMK04832, LMK04828, LMK04821, and LMK04826 with information on JESD204B, device clocks, SYSREF, analog and digital delays. Noise performance analysis in closed loop for VCO0 and VCO1 with phase noise values, offset frequencies, and figure of merit.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

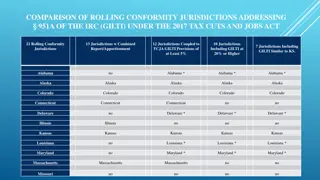

General specifications Parameter LMK04832 LMK04828 LMK04821 LMK04826 VCO frequency range VCO0: 2440 to 2580 MHz VCO1: 2945 to 3255 MHz VCO0: 2370 to 2630 MHz VCO1: 2920 to 3080 MHz VCO0: 1930 to 2075 MHz VCO1: 2920 to 3080 MHz VCO0: 1840 to 1970 MHz VCO1: 2440 to 2505 MHz Maximum output frequency generated by internal VCO 3255 MHz 3080 MHz 2075 MHz 2505 MHz VCO1 divider value No No 2 to 8 No Maximum input frequency @ CLKinx 750 MHz 750 MHz Maximum input frequency for EXT VCO or Distribution 3250 MHz 3100 MHz Number of inputs 3 (Dual loop operation) 4 (Single loop operation) 3 (Dual loop operation) 1 (Single loop operation) Maximum PLL2 PFD 320 MHz 155 MHz Supply voltage 3.15 V to 3.45 V 3.15 V to 3.45 V -40 C to 85 C -40 C to 85 C Operating temperature Package WQFN (64) - 9 mm x 9 mm WQFN (64) - 9 mm x 9 mm Pin to pin compatible Yes CML, HSDS, LCPECL, LVCMOS, LVDS, LVPECL Yes Output format HSDS, LCPECL, LVCMOS, LVDS, LVPECL

Clock output formats, output dividers and delays Parameter LMK04832 LMK04828 LMK04821 LMK04826 JESD204B Device clock SYSREF pairs 7 7 Device clock and SYSREF Mux to any output Yes Only Device clocks CML Output Format 7 outputs No Differential Output Format (LVDS / LVPECL) 14+1* outputs 14+1* outputs LVCMOS Output Format 18 + 2* 3.3-V LVCMOS 2* 3.3-V LVCMOS VCO to Device clock divider 1 to 1023 1 to 32 VCO to SYSREF divider 8 to 8191 8 to 8191 Device clock analog delay No 25 ps steps** (0 to 575 ps total delay) SYSREF analog delay 21 ps steps 150 ps steps Device clock digital delay 8 to 1023 VCO cycles, step size: cycle 4 to 32 VCO cycles, step size: cycle SYSREF digital delay 1.5 to 11 VCO cycles, step size: cycle 1.5 to 11 VCO cycles, step size: cycle Both PLL R-divider reset Yes No * +1 differential or +2 LVCMOS outputs from OSCout pins ** Device clock analog delay degrades the noise floor between 1-6dB across frequency

Noise Performance Closed Loop PN @ 245.76 MHz (VCO0) Closed Loop PN @ 245.76 MHz (VCO1) Closed Loop PN (dBc/Hz) @ 245.76 MHz LMK04832 LMK04828 LMK04821 LMK04826 LMK04826 LMK04832 LMK04828 LMK04821 Offset Freq (kHz) -120 -120 VCO0/ VCO1 LMK04832 LMK04828 LMK04821 LMK04826 -125 -125 Phase Noise (dBc/Hz) Phase Noise (dBc/Hz) 1 -125 -124.3 -126.9 - -130 -130 10 -134 -134.7 -133.5 -134.8 -135 -135 VCO0 100 -137 -136.5 -135.4 -135.4 -140 -140 1000 -154 -148.4 -149.8 -148.6 -145 -145 -150 -150 1 -125 -124.2 -126.8 - -155 -155 10 -135 -134.4 -133.4 -134.3 VCO1 -160 -160 100 -137 -135.2 -135.4 -133.7 1000 10000 100000 1000000 1000 10000 100000 1000000 1000 -151 -151.5 -151.8 -153.6 Offset Frequency (Hz) Offset Frequency (Hz) Figure of Merit PLL 1/f Noise* Noise floor @ 245.76 MHz -218 -110 -156 Noise Floor (dBc/Hz) 1/f Noise 9dBc/Hz) -220 FOM (dBc/Hz) -115 -158 -222 -224 -120 -160 -226 -228 -125 -162 -230 -232 -130 -164 LMK04832 LMK0482x LMK04832 LMK0482x LMK04832 LMK04828 LMK04821 LMK04826 PLL1 -225 -223 PLL1 VCO0 -119 -118 -163 -162.5 -162 -162 PLL2 -230 -227 PLL2 VCO1 -128 -121 -163 -161.1 -158.9 -160.8 *10 kHz offset normalized to 1 GHz output * LVPECL20 with 240 (20 MHz offset)

Noise performance (Contd..) LMK0482x LMK04832