Overview of Distributed Systems: Characteristics, Classification, Computation, Communication, and Fault Models

Characterizing Distributed Systems: Multiple autonomous computers with CPUs, memory, storage, and I/O paths, interconnected geographically, shared state, global invariants. Classifying Distributed Systems: Based on synchrony, communication medium, fault models like crash and Byzantine failures. Comp

9 views • 126 slides

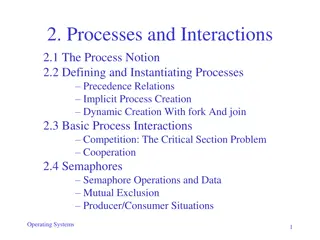

Processes and Interactions

Processes in operating systems involve executing programs on CPUs, with each process having its own CPU. Processes run concurrently and can cooperate or compete for resources. Defining, creating, and managing processes is crucial for system efficiency and performance. Precedence relations, semaphore

1 views • 38 slides

Understanding Computer Components and Binary Numbers in Computing

Computer components like the case, power supply unit, motherboard, and storage devices play crucial roles in a computer system. CPUs consist of essential parts like the ALU, control unit, and registers. Binary numbers, a base-2 numbering system, simplify data representation and processing in computi

1 views • 44 slides

Understanding Threads in Computing

Exploring the concepts of parallel, distributed, and concurrent computing processes and how threads, cores, and CPUs work together. Delve into the terminology, implementation in Java and C#, synchronization, and the importance of leveraging multiple cores for enhanced performance.

0 views • 24 slides

Technology Update and Market Trends Overview

Explore the latest advancements in technology update, general market trends, major players in the data center industry, future fabrication processes, server market shifts towards AI and cloud, the rise of liquid cooling, CPU developments, and trends in CPUs with increasing core counts and new archit

0 views • 28 slides

Overview of Distributed Operating Systems

Distributed Operating Systems (DOS) manage computer resources and provide users with convenient interfaces. Unlike centralized systems, DOS runs on multiple independent CPUs and prioritizes software over hardware. It ensures transparency and fault tolerance, with a focus on software error handling.

1 views • 36 slides

Exploring Automotive Networks and ECUs in the World of SOME/IP

In the realm of automotive networks, Electronic Control Units (ECUs) play a vital role in managing various aspects of a vehicle's systems. Modern ECUs are sophisticated with Systems on Chip (SoCs) containing CPUs, memory, I/O ports, and communication interfaces. With examples of different types of E

1 views • 101 slides

Understanding System Management RAM (SMRAM) in x86 Architecture

Delve into the internals of System Management RAM (SMRAM) in x86 architecture, exploring how the processor switches to SMRAM upon entering System Management Mode (SMM). Learn about SMBASE, the base address of SMRAM, and how the address space layout is defined. Discover how SMBASE and SMRAM are essen

1 views • 43 slides

Stack Organization in Computer Systems

A stack is an ordered linear list where insertions and deletions occur at one end, known as the top. It follows the Last In First Out (LIFO) access method and is commonly used in CPUs. Key operations include Push (inserting) and Pop (deleting) items from the stack. Applications include evaluating ma

0 views • 5 slides

Understanding Interrupts in Embedded Systems

In embedded systems, interrupts play a crucial role in letting peripherals notify the CPU of state changes. They are events external to the current process that disrupt the normal flow of instruction execution, typically generated by hardware devices. By using interrupts, CPUs can efficiently handle

1 views • 12 slides

Understanding Memory Virtualization in Operating Systems

Memory virtualization in operating systems involves mapping guest addresses to host addresses with an added level of indirection managed by the hypervisor. Virtualization extensions in x86 processors enhance efficiency by allowing safe execution of guest code in Ring 0 through supervisor mode. The a

1 views • 28 slides

Understanding Shared Memory Architectures and Cache Coherence

Shared memory architectures involve multiple CPUs sharing one memory with a global address space, with challenges like the cache coherence problem. This summary delves into UMA and NUMA architectures, addressing issues like memory latency and bandwidth, as well as the bus-based UMA and NUMA shared m

0 views • 27 slides

Understanding PCI Expansion ROMs in x86 Systems

This content delves into the intricacies of PCI Expansion ROMs (XROMs) in x86 systems. It covers the basics of XROMs, their execution during the boot process, configuration through Expansion ROM Base Address Register, and handling in PCI and PCIe devices. The role of BIOS in initializing XROMs and t

4 views • 21 slides

Understanding PCI/PCIe Expansion ROMs in x86 Systems

Explore the internals of PCI/PCIe Expansion ROMs (XROMs) in x86 systems, examining their role as executable code located on PCI devices, handling by BIOS during boot, configuration via Expansion ROM Base Address Register, and differences on legacy versus modern systems.

4 views • 21 slides

Understanding System Management Mode (SMM) in x86 Processors

System Management Mode (SMM) is a highly privileged mode in x86 processors that provides an isolated environment for critical system operations like power management and hardware control. When the processor enters SMM, it suspends all other tasks and runs proprietary OEM code. Protecting SMM is cruc

1 views • 26 slides

Understanding the Need for Neural Network Accelerators in Modern Systems

Neural network accelerators are essential due to the computational demands of models like VGG-16, emphasizing the significance of convolution and fully connected layers. Spatial mapping of compute units highlights peak throughput, with memory access often becoming the bottleneck. Addressing over 300

0 views • 21 slides

Optimizing User-Space Network Services with F-Stack and FreeBSD TCP/IP Stack

F-Stack, a user-space network service using DPDK and FreeBSD TCP/IP stack, addresses challenges in handling service traffic like CDN and live streaming. By leveraging 25GbE, 40GbE, and 100GbE NICs, coupled with multi-core CPUs and kernel bypass techniques, F-Stack overcomes bottlenecks between user

1 views • 17 slides

Understanding Modern GPU Computing: A Historical Overview

Delve into the fascinating history of Graphic Processing Units (GPUs), from the era of CPU-dominated graphics computation to the introduction of 3D accelerator cards, and the evolution of GPU architectures like NVIDIA Volta-based GV100. Explore the peak performance comparison between CPUs and GPUs,

5 views • 20 slides

Understanding Flash Descriptor in x86 Systems

Explore the internals of the Flash Descriptor in x86 systems, essential for BIOS and system management mode. Learn about SPI regions, determining SPI regions, flash protection mechanisms, and the structure of the Flash Descriptor for Intel systems. Complete with images and detailed explanations.

5 views • 30 slides

FPGA Accelerator Design Principles and Performance Snapshot

This content explores the principles behind FPGA accelerator design, highlighting the extreme pipelining via systolic arrays that enables FPGAs to achieve high speeds despite lower clock frequencies compared to CPUs and GPUs. It delves into the application of Flynn's Taxonomy, performance snapshots

0 views • 17 slides

Comprehensive Guide to IEC1131-3 Ladder Diagram Programming

The origins of ladder diagram programming trace back to the graphical representation of electrical control systems, evolving from relay logic to logic circuits and finally incorporating CPUs for control decisions. A ladder diagram consists of rungs containing input and output instructions, executing

0 views • 21 slides

Understanding Virtualization in Modern Systems

Virtualization plays a crucial role in modern systems by improving portability, security, and efficient resource utilization. Historical uses, examples like IBM VM/370, and benefits in cloud environments are discussed. The working of virtualization, including naive software interpreters and protecte

1 views • 18 slides

Understanding Shared Memory Architectures and Cache Coherence

Shared memory architectures involve multiple CPUs accessing a common memory, leading to challenges like the cache coherence problem. This article delves into different types of shared memory architectures, such as UMA and NUMA, and explores the cache coherence issue and protocols. It also highlights

2 views • 27 slides

15-213 Recitation: Bomb Lab Overview and Tips

This content covers the Bomb Lab exercise in x86-64 assembly code and GDB debugging techniques. It explains the purpose of Bomb Lab, downloading the bomb, detonating the bomb, hints for solving phases, and x86-64 Linux register usage. The material emphasizes the importance of using GDB for efficient

1 views • 42 slides

A Comprehensive Guide to Computers and Their Evolution

Exploring the world of computers from its inception to modern-day innovations. Understand the history, functions, and advancements in computer technology, including details on CPUs, memory, laptops, and mobile devices like phones and tablets.

5 views • 10 slides

Understanding x86-64 Procedures and Data Structures

This content provides insights into x86-64 programming, covering topics such as procedures, integer registers, stack frames, locals in the red zone, interesting features of stack frames, arrays, multi-dimensional structures, and more. It dives into the usage conventions of integer registers, the all

0 views • 44 slides

Memory Consistency Models and Sequential Consistency in Computer Architecture

Memory consistency models play a crucial role in ensuring proper synchronization and ordering of memory references in computer systems. Sequential consistency, introduced by Lamport in 1979, treats processors as interleaved processes on a shared CPU and requires all references to fit into a global o

1 views • 64 slides

Enhancing I/O Performance on SMT Processors in Cloud Environments

Improving I/O performance and efficiency on Simultaneous Multi-Threading (SMT) processors in virtualized clouds is crucial for maximizing system throughput and resource utilization. The vSMT-IO approach focuses on efficiently scheduling I/O workloads on SMT CPUs by making them "dormant" on hardware

0 views • 31 slides

DirectLOGIC Communications Training Overview

Explore the technical training communications for Do-more DirectLOGIC systems, focusing on setting up communication between DL Servers and Clients using built-in Ethernet ports and ECOM100 modules. Learn about communication configurations, memory allocation, and parameter settings to establish effec

0 views • 28 slides

Understanding Lower Bounds in the Cell Probe Model

Exploring the concept of lower bounds for static data structures, this content delves into the tradeoffs between query time and space efficiency. It discusses the need for proving lower bounds, the model of data structures, and how CPUs access memory in computational devices. Kasper Green Larsen fro

0 views • 45 slides

Framework for One-sided RDMA Multicast in Data Center Group Communications

This paper explores the implementation of one-sided RDMA multicast in data center group communications, highlighting the benefits of offloading network I/O from CPUs and unique connection parameters for efficient multicast operations. The research addresses the challenges of enabling one-sided RDMA

0 views • 11 slides

Introduction to Computers: Understanding Hardware and Input Devices

Computers are electronic devices that process input to produce information. They consist of hardware components like CPUs, input/output units, and memory. Input devices such as keyboards, mice, and scanners help translate human-readable data for computer processing.

0 views • 11 slides

Introduction to Y86 Instruction Set Architecture

Y86 Instruction Set Architecture is a simplified pseudo-language based on x86 (IA-32) architecture. It involves implementing the Fetch-Decode-Execute cycle, where instructions are fetched from memory, decoded, and executed. The Y86 ISA offers a simpler set of instructions and formats compared to x86

0 views • 25 slides

Understanding Random Numbers in Computers

Explore the concept of true random numbers versus pseudorandom numbers in computers. Learn how pseudorandom numbers are generated algorithmically but predictable, while true random numbers are derived from physical phenomena like radioactive decay. Discover the relevance of high-entropy pseudorandom

0 views • 57 slides

Understanding SMI Suppression in x86 BIOS Management

Delve into the intricacies of SMI Suppression in x86 BIOS and System Management Mode internals, where SMI stands as a crucial defense mechanism to safeguard the BIOS flash from unauthorized modifications. Explore the impact of suppressing SMI generation and learn about the SMI_EN register's role in

1 views • 18 slides

Understanding Interrupt Processing Sequence in X86 Processors

X86 processors have 256 software interrupts, functioning similarly to a CALL instruction. When an INT n instruction is executed, the processor follows a sequence involving pushing the flag register, clearing flags, finding the correct ISR address, and transferring CPU control. Special interrupts lik

0 views • 10 slides

Understanding X86 ISA Flags in System Security

This article delves into the details of various flags in the X86 ISA architecture, such as CF (Carry Flag), PF (Parity Flag), AF (Auxiliary Flag), ZF (Zero Flag), SF (Sign Flag), TF (Trace Flag), IF (Interrupt Flag), DF (Direction Flag), OF (Overflow Flag), and IOPL (Input Output Privilege Level). T

0 views • 16 slides

Understanding x86-64 Stack and Register Usage at Carnegie Mellon

Explore the concepts of stack management, function invocation, and register usage in x86-64 architecture as taught in Carnegie Mellon's 15-213 recitation on Attack Lab. Learn about stack operations, caller vs. callee functions, and the conventions for using registers effectively. Gain insights into

0 views • 26 slides

Software Design Considerations for Multicore CPUs

Discussion on performance issues with modern multi-core CPUs, focusing on higher-end chips and boards. Exploring the concept of cores, chips, and boards in the context of multicore CPUs and their memory architectures.

0 views • 31 slides

Hardware Performance Monitoring with Kernel Modules

This document explores the use of hardware performance counters and cycle counting on x86 and ARM architectures for monitoring and analyzing system performance. It covers topics such as the utilization of hardware counters, cycle counting on x86 processors, and the ARM Performance Monitor Unit (PMU)

0 views • 12 slides