❤Book⚡[PDF]✔ The Apollo Guidance Computer: Architecture and Operation (Springer

\"COPY LINK HERE ; https:\/\/getpdf.readbooks.link\/1441908765\n\nDownload Book [PDF] The Apollo Guidance Computer: Architecture and Operation (Springer Praxis Books) | The Apollo Guidance Computer: Architecture and Operation (Springer Praxis Books)\n\"\n

2 views • 6 slides

Pipelined Reasoning Of Verifiers Enabling Robust Systems (PROVERS)

The PROVERS program aims to develop automated formal methods tools integrated into software development pipelines to enable the incremental production and maintenance of high-assurance national security systems. Addressing DoD challenges and vulnerabilities in weapon systems, the initiative emphasiz

3 views • 25 slides

Understanding Reactor Campaign in Nuclear Power Operations

Reactor campaign in nuclear power operations is crucial for ensuring safe and efficient reactor power operation. It involves managing reactivity margin, fuel residence time, nominal power, and effective days of operation. Reactor campaigns are influenced by various factors such as fuel elements' res

1 views • 64 slides

Enhanced Multi-Link Single Radio Operation Proposal

The proposal discusses an enhanced mode of operation for single radio non-AP MLDs to enable multi-link operation, improving throughput and reducing latency. It addresses challenges in busy network environments, aiming to achieve low latency benefits similar to concurrent dual radio setups. The propo

0 views • 22 slides

Specific Controls Requirements for p-Linac at GSI Helmholtzzentrum

Explore the specific control requirements for the p-Linac at GSI Helmholtzzentrum, including detailed information on beam energy, design current, RF power, and related devices. Get insights into the overall design, main devices, FAIR primary beam chain, booster operation, and parallel operation exam

0 views • 13 slides

Considerations on Coordinated OFDMA Operation in IEEE 802.11

The document discusses the Coordinated OFDMA (C-OFDMA) operation as a part of Multi-AP coordination schemes within the IEEE 802.11 standard. It covers resource allocation options, topology considerations, resource allocation methods, capability announcement procedures, and negotiation processes betw

0 views • 15 slides

Discussion on FDM Operation for SL and Uu in Licensed Band at 3GPP TSG-RAN WG4#98-e Meeting

The 3GPP TSG-RAN WG4#98-e meeting discussed introducing Frequency Division Multiplexing (FDM) operation for Uplink (UL) and Secondary Link (SL) in licensed bands. Topics included frequency separation, power control, RF architecture, and intra-band Carrier Aggregation (CA). Options were considered fo

0 views • 10 slides

PowerPC Architecture Overview and Evolution

PowerPC is a RISC instruction set architecture developed by IBM in collaboration with Apple and Motorola in the early 1990s. It is based on IBM's POWER architecture, offering both 32-bit and 64-bit processors popular in embedded systems. The architecture emphasizes a reduced set of pipelined instruc

2 views • 13 slides

Understanding Multi-AP Operation in IEEE 802.11-20-0617/r3

Explore the basic definitions and key features of Multi-AP operation in the IEEE 802.11 standard. Learn about Multi-AP Candidate Set (M-AP-CS) and Multi-AP Operation Set (M-AP-OS) along with their participants and formation. Delve into the concepts of Coordinator AP, Coordinated AP(s), and reliable

0 views • 19 slides

Understanding Multi-Band Multi-Channel Concept in IEEE 802.11be

Exploring the benefits of Multi-Band Multi-Channel (MBMC) operation in IEEE 802.11be, this study delves into the efficient use of spectrum, increased data rates, and network load balancing. It also discusses the envisioned usage models and compares Single Band Operation with Multi-Band Operation, hi

1 views • 20 slides

Understanding TCP Reliability and Pipelined Delivery

This lecture delves into the concepts of TCP reliability and pipelined data delivery, emphasizing the need for mechanisms to ensure data integrity and accuracy. It covers error detection, handling delayed and dropped packets, setting retransmission timeouts (RTO), coping with packet duplication and

0 views • 35 slides

Overview of Multi-AP Operation in IEEE 802.11be

The document discusses the unique feature of multi-AP operation in IEEE 802.11be, emphasizing the performance benefits in various deployments. It addresses the need for AP-to-AP communication, the concept of anchor APs, interfaces for inter-AP communication, and backhaul options. The importance of f

0 views • 13 slides

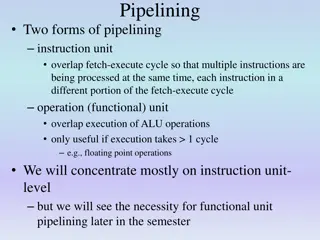

Understanding Pipelining in Computer Architecture

Pipelining in computer architecture involves overlapping fetch-execute cycles to process multiple instructions concurrently. It utilizes stages, latches, and throughput to enhance CPU performance. Different forms of pipelining, stage-related terms, and the transition from non-pipelined to pipelined

0 views • 64 slides

Considerations for Relay Operation in Next Generation Wi-Fi Networks

In this document, considerations and use cases for relay operation in next generation Wi-Fi networks are discussed. The authors provide insights into the improvements in reliability and throughput, focusing on the benefits of relay features in various scenarios such as smart home devices and automot

0 views • 11 slides

Efficient Class B Amplifier Operation and Power Calculation

Class B amplifiers offer greater efficiency compared to single transistor Class A operation. This article covers the push-pull operation of Class B transistors, input DC power calculations, connecting push-pull amplifiers to loads, output AC power measurement, efficiency calculation, and power dissi

0 views • 28 slides

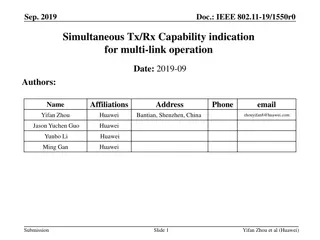

IEEE 802.11-19/1550r0: Simultaneous Tx/Rx Capability Indication for Multi-Link Operation

This document discusses the simultaneous Tx/Rx capability indication for multi-link operation in IEEE 802.11-19/1550r0. It covers scenarios where link selection depends on link capabilities, actions needed based on Tx/Rx capabilities, and methods to indicate simultaneous operation. The importance of

4 views • 10 slides

Understanding Pipelined Control in Processor Architecture

Explore the intricacies of pipelined control in processor design, detailing the control signals required at each stage of the pipeline. Learn about data hazards, forwarding, and stalling techniques to ensure efficient instruction execution. Dive into the concept of optimized control values for strea

0 views • 16 slides

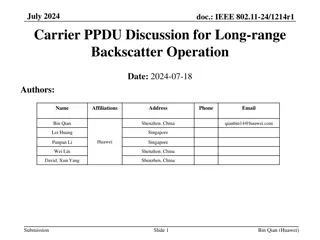

Carrier PPDU Discussion for Long-range Backscatter Operation in IEEE 802.11-24

This document discusses the use of Carrier PPDU for long-range backscatter operation in IEEE 802.11-24 standard. It covers topics such as close-range and long-range backscatter in AMP, reader PPDU for close-range operation, and different topologies to support long-range backscatter. The content incl

0 views • 14 slides

PipeSwitch: Fast Context Switching for Deep Learning Applications

PipeSwitch introduces fast pipelined context switching for deep learning applications, aiming to enable GPU-efficient multiplexing of multiple DL tasks with fine-grained time-sharing. The goal is to achieve millisecond-scale context switching overhead and high throughput, addressing the challenges o

1 views • 38 slides

Lateral Ear Canal Resection (Zepp's Operation) by Dr. Gulshan Kumar

Lateral ear canal resection, also known as Zepp's operation, is a surgical procedure performed by Dr. Gulshan Kumar, MVSc, PhD. This operation involves the removal of a portion of the lateral ear canal to treat various ear conditions. The images show different stages of the procedure, providing a vi

0 views • 6 slides

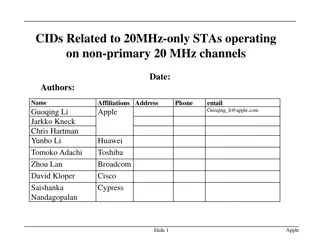

Proposal for Enhancing Operation of 20MHz-Only STAs on Non-Primary Channels

The proposal aims to clarify how 20MHz-only STAs can operate on non-primary 20MHz channels, introducing protocol components and considerations for seamless operation. It suggests allowing optional operation on secondary channels and specifies signaling, behavior norms, and capabilities for optimal p

0 views • 19 slides

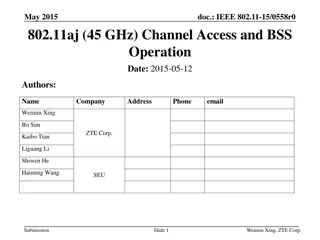

802.11aj 45 GHz Channel Access and BSS Operation Framework Proposal

This document outlines a proposal for channel operation and BSS operation in the 45 GHz frequency bands for 802.11aj in China. It includes details on channelization, spectrum allocation, maximum transmit power, and BSS configuration rules. The aim is to meet the functional requirements specified whi

0 views • 32 slides

Reducing Amperage in Pot Operation: Alumina Shortage Concern

The group discussion focuses on pot operation at reduced amperage due to a shortage of alumina. Details include normal operation specifications, calculations for operating voltage at 300 kA, breakdown of new pot voltages, adjustments in ACD and bath height at 300 kA, and the amount of bath needed to

0 views • 17 slides

Discussion on FDM Operation and Frequency Separation in Licensed Bands

Discussion during the RAN4#98-e meeting focused on the introduction of FDM operation of UL and SL in licensed bands. Topics included carrier options, frequency separation in adjacent and non-adjacent channels, power issues, and recommendations for further investigation. The meeting explored options

0 views • 9 slides

Long-term Operation of Superconducting Triplet Quadrupoles (STQ) with Cryocoolers at RIKEN

Introduction to the operational experiences, maintenance, and long-term operation of the Superconducting Triplet Quadrupoles (STQ) with cryocoolers for the BigRIPS In-flight Separator at RIKEN. Details include standard operation of SC magnets, unique features of BigRIPS and RI-beam delivery lines, S

0 views • 16 slides

Overview of CRWG Issues and Requests for 10Hz Operation and APS Role

This document discusses CRWG issues related to the 10Hz operation, including the need for 10Hz collision operation, parameter sets for different energy levels, and the addition of a beamline for 10Hz operation. It also covers the APS role in commissioning positron facilities and its usefulness for v

0 views • 14 slides

Energy Harvesting Operation Procedures for AMP Devices in WLAN

This submission delves into the operation procedures of AMP devices in WLAN setups, focusing on energy harvesting techniques for various power sources like solar and RF. It details the operation procedures for devices with and without energy storage, highlighting configurations for day and night use

0 views • 8 slides

Dynamic Bloom Filter Operation for Pre-Association Service Discovery

This document outlines a proposal for a Dynamic Bloom Filter Operation as part of a Pre-Association Service Discovery protocol to efficiently and quickly identify services offered by devices in a network. The design goals include efficiency, speed of discovery, and scalability. Challenges addressed

0 views • 15 slides

Understanding Operation Research: A Brief Overview

Operation Research (O.R.) is a scientific method applied to aid management in decision-making through quantitative analysis. Originating during World War II, O.R. helps in finding optimal solutions to system operation problems. It involves the use of scientific methods and tools to tackle various ma

0 views • 140 slides

Understanding Pipeline Hazards in Computer Architecture

Pipeline hazards in computer architecture are classified into three categories: structural, data, and control hazards. Structural hazards occur due to conflicts in hardware resources, data hazards stem from dependencies between instructions, and control hazards arise from branching instructions. The

0 views • 42 slides

Principles and Importance of Co-operation in Agriculture

Co-operation in agriculture involves voluntary association for common economic interest. It is based on equality and principles like open association, self-help, service, and neutrality. Maxims of co-operation emphasize solidarity and mutual support. Dr. J.P. Singh, Associate Professor at SGRRU, dis

0 views • 6 slides

Understanding Cryogenics: Torus 4K Operation and Recovery

This lesson delves into the intricate details of Torus 4K operation and recovery in cryogenics. Topics covered include supply from ESR main compressors, cold box, valve box, helium distribution, supercritical helium flow, back pressure control, and more. Special notes emphasize the importance of ver

0 views • 31 slides

Understanding Advanced Computer Architecture in Parallel Computing

Covering topics like Instruction-Set Architecture (ISA), 5-stage pipeline, and Pipelined instructions, this course delves into the intricacies of advanced computer architecture, with a focus on achieving high performance by optimizing data flow to execution units. The course provides insights into t

0 views • 12 slides

Introduction to Parallel Computing Concepts

Exploring the concepts of threads, pipelining, and dependence in parallel computing. Discussions on why multiple threads are beneficial, pipelined instructions, and the challenges of dependencies in executing instructions sequentially. Delve into Simultaneous Multithreading (SMT) and its advantages

0 views • 9 slides

Constructive Computer Architecture: Multistage Pipelined Processors

Explore the concepts of multistage pipelined processors and modular refinement in computer architecture as discussed by Arvind and his team at the Computer Science & Artificial Intelligence Lab, Massachusetts Institute of Technology. The content delves into the design and implementation of a 3-stage

0 views • 28 slides

Data Hazards in Pipelined Processors: Understanding and Mitigation

Explore the concept of data hazards in pipelined processors, focusing on read-after-write (RAW) hazards and their impact on pipeline performance. Learn strategies to mitigate data hazards, such as using a scoreboard to track instructions and stall the Fetch stage when necessary. Discover how adjusti

0 views • 23 slides

Understanding the Basics of Multi-Stage Architecture in CPU Design

The article explains the fundamentals of a multi-stage digital processing system in computer organization, focusing on the central processing unit (CPU). It covers topics such as instruction execution, processor building blocks, and the benefits of pipelined operation. Concepts like fetching, decodi

0 views • 42 slides

Understanding Pipelined Implementation in Computer Architecture

Learn about the general principles of pipelining, challenges in creating a pipelined Y86-64 processor, real-world pipeline examples like car washes, computational examples, 3-way pipelined version details, pipeline diagrams, operating a pipeline, and limitations of pipelining. Explore topics such as

0 views • 32 slides

Understanding Pipelined Implementation in Computer Architecture

This resource delves into the concepts of pipelining in computer architecture, exploring the general principles, real-world analogies, computational examples, and the operation of a pipeline. It covers the difficulties in creating pipelined processors, handling data and control hazards, and showcase

0 views • 32 slides

Trade-offs in Floating Point Accumulation: Balancing Accuracy, Cost, and Performance

When designing floating point accumulation systems, achieving high throughput and accuracy presents a challenging trade-off. Inconsistent accuracy due to data dependencies can lead to significant errors in results. Strategies such as compensated summation or using extended precision adders can help

0 views • 11 slides

![❤Book⚡[PDF]✔ The Apollo Guidance Computer: Architecture and Operation (Springer](/thumb/21611/book-pdf-the-apollo-guidance-computer-architecture-and-operation-springer.jpg)