SN65DSI85-Q1 Layout Review

In-depth analysis and review of the layout design for the 2026 Nissan CDC Headunit utilizing the SN65DSI85-Q1 system. The review includes detailed information on various layers such as Layer1 to Layer10, the schematic representation, and the block diagram outlining the PMIC Cluster ASIL-B setup. Key

0 views • 13 slides

Update on Drought Monitoring Indicators and Indices at SERCOM-3 Conference

The SERCOM-3 conference held in Bali, Indonesia, discussed the adoption of additional drought indicators and indices for use by National Meteorological and Hydrological Services (NMHS). The update to the Global Drought Classification System (GDCS) included recommendations for the use of standardized

0 views • 4 slides

Understanding VA Privacy Issues and Sensitive Information

Explore the complex landscape of VA privacy issues, including data relationships, sensitive personal information (SPI), personally identifiable information (PII), individually identifiable information (III), and individually identifiable health information (IIHI). Learn about the roles and responsib

0 views • 29 slides

Patch Bundle Mode Walkthrough for Device Configuration

Explore the Patch Bundle Mode walkthrough consisting of flowcharts and pseudo code examples for controlling a device's patch mode, downloading configurations, and changing device modes. The content provides a detailed guide on using commands to initiate patch burst mode, specify I2C addresses, and t

0 views • 4 slides

Comparison of SPI and I2C Communication in Embedded Systems

SPI and I2C are two common communication protocols used in embedded systems. SPI offers fast and easy point-to-point connections with no addressing needed, while I2C allows connecting multiple peripherals with just two wires. SPI has pros such as fast data transfer but cons like complexity with mult

1 views • 17 slides

Understanding Flash Descriptor in x86 Systems

Explore the internals of the Flash Descriptor in x86 systems, essential for BIOS and system management mode. Learn about SPI regions, determining SPI regions, flash protection mechanisms, and the structure of the Flash Descriptor for Intel systems. Complete with images and detailed explanations.

5 views • 30 slides

Designing a Network-Controlled Railway System with Human Monitoring

Our project aims to design a network-controlled railway system that allows for human intervention and monitoring. The system consists of a main control station, multiple trains, and a communication and power infrastructure. The main control station includes a main microcontroller connecting to a PC,

2 views • 29 slides

Understanding BIOS Flash and System Management Mode Internals

Dive into the intricacies of BIOS flash and system management mode internals, exploring SPI flash technology, attacker persistence strategies, Copernicus vulnerability scanning results, BIOS flash locations, and boot BIOS flash configurations. Uncover the significance of hardware pins in determining

0 views • 28 slides

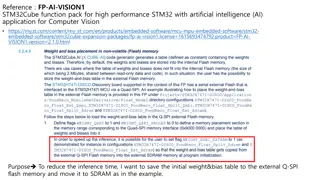

Optimizing Inference Time by Utilizing External Memory on STM32Cube for AI Applications

The user is exploring ways to reduce inference time by storing initial weight and bias tables in external Q-SPI flash memory and transferring them to SDRAM for AI applications on STM32Cube. They have questions regarding the performance differences between internal flash memory and external memory, r

0 views • 4 slides

Understanding I2C Bus Interface and Protocol

I2C, short for Inter-Integrated Circuit, is a serial protocol with a two-wire interface designed by Philips. It allows communication between master and slave devices using start and stop conditions. Each slave device has a unique address, and data transfer occurs in serial 8-bit packets at varying s

0 views • 11 slides