Logic Families

Logic families such as Diode Logic (DL), Resistor-Transistor Logic (RTL), and Diode-Transistor Logic (DTL) each have distinct capabilities and limitations when it comes to performing logic functions. While DL gates are simple and inexpensive but limited in functionality, RTL gates offer both normal

1 views • 22 slides

Understanding FSMD: FSM with Datapath in FPGA Design

Explore the concept of Finite State Machine with Datapath (FSMD) in FPGA design, as discussed in the lecture at George Mason University. Learn about translating sequential algorithms into hardware, using registers and control paths to simulate variables, and realizing systems through RTL design. Dis

1 views • 54 slides

DIY Budget APRS I-Gate & Digipeater Setup

Learn how to build your own APRS I-Gate & Digipeater without overspending. Understand the functions of a Digipeater and an I-Gate, and gather the necessary components like RTL-SDR kits, Baofeng radio, Raspberry Pi, and antennas. Connect all the components to create a functional I-Gate and Digipeater

0 views • 11 slides

Introduction to Ruckus and SURF by TID-AIR Electronics

Ruckus and SURF are key frameworks developed by TID-AIR Electronics. Ruckus, a Vivado build system, simplifies Vivado project environments and integrates git repositories. Meanwhile, SURF, the SLAC Ultimate RTL Framework, offers various libraries for firmware development. Both are controlled and mai

0 views • 24 slides

Enhancing Off-chip Bandwidth Utilization for Improved System Performance

Efficiently coordinating off-chip read/write bandwidth through the Bandwidth-aware LLC proposal yields a 12% performance improvement in an 8-core system across multiple workloads. This approach optimizes DRAM read latency, surpassing existing policies and filling performance gaps while confirming lo

1 views • 36 slides

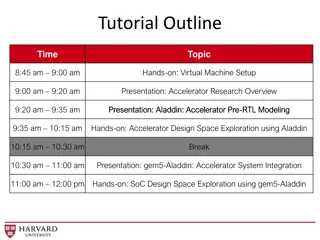

Accelerator Design Space Exploration Tutorial

This tutorial covers hands-on activities and presentations on virtual machine setup, accelerator research overview, RTL modeling, design space exploration using Aladdin, gem5-Aladdin for system integration, and SoC design space exploration. Aladdin, a pre-RTL power-performance accelerator simulator,

0 views • 52 slides

Understanding High-Level Synthesis (HLS) Process

High-Level Synthesis (HLS) is an automated design process that converts functional specifications into optimized hardware implementations at the Register-Transfer Level (RTL). It offers efficient hardware development using software specifications and program logic synthesis. HLS tools such as Verilo

0 views • 33 slides