ANALOG AND DIGITAL ELECTRONICS 21CS33

Explore the world of analog and digital electronics through the lens of registers, counters, and flip-flops. Dive deep into the operation of these components, learn how to transfer data between registers, build and analyze shift registers, construct timing diagrams, and understand binary counters. D

0 views • 112 slides

COMPUTER ORGANISATION Register Transfer Language

Register Transfer Language is a symbolic notation used to describe the micro-operations transferring data among registers in computer organisation. It signifies the availability of hardware logic circuits to perform specified micro-operations and transfer results between registers. Register Transfer

6 views • 7 slides

Implementing Address Spaces: Base + Limit Registers

Address spaces, base + limit registers, and contiguous allocation are essential concepts in operating systems. Real mode memory addresses lack isolation between processes and pose limitations on multitasking. Virtual memory introduces virtual address spaces, requiring translation to physical address

3 views • 11 slides

Understanding Computer Architecture: CPU Structure and Function

Delve into the intricate world of computer architecture with Prof. Dr. Nizamettin AYDIN as your guide. Explore topics such as CPU structure, registers, instruction cycles, data flow, pipelining, and handling conditional branches. Gain insights into the responsibilities of a CPU, internal structures,

0 views • 39 slides

Understanding Basic Input/Output Operations in Computer Organization

Basic Input/Output Operations are essential functions in computer systems that involve transferring data between processors and external devices like keyboards and displays. This task requires synchronization mechanisms due to differences in processing speeds. The process involves reading characters

0 views • 11 slides

Introduction to Intel Assembly Language for x86 Processors

Intel Assembly Language is a low-level programming language designed for Intel 8086 processors and their successors. It features a CISC instruction set, special purpose registers, memory-register operations, and various addressing modes. The language employs mnemonics to represent instructions, with

2 views • 12 slides

Basic Computer Organization and Design - Timing and Control

The timing of all registers in a basic computer is governed by a master clock generator, with clock pulses controlling the flip-flops and registers in the system. Two main types of control organization are Hardwired Control and Micro-programmed Control. The former uses digital circuitry like gates a

1 views • 4 slides

Understanding Flag Registers in Microprocessor 8086

This content discusses the flag registers in the Microprocessor 8086, covering conditional flags such as Carry Flag (CF), Auxiliary Flag (AF), Parity Flag (PF), Zero Flag (ZF), Sign Flag (SF), and Overflow Flag (OF), as well as control flags including Trap Flag (TP), Interrupt Flag (IF), and Directi

0 views • 23 slides

Overview of MIPS Arithmetic and Logic Instructions in COE 301

MIPS Architecture consists of R-Type and I-Type instruction formats for arithmetic, logical, shift, and immediate constant operations. It includes a variety of general-purpose registers and specific units for execution, floating-point operations, and memory handling. The presentation outlines the st

2 views • 29 slides

Understanding Shift Registers in Digital Electronics

Shift registers are a fundamental concept in digital electronics where binary numbers are shifted from one flip-flop to the next. They come in various types like SISO, SIPO, PISO, and PIPO, serving different purposes such as delay lines, data converters, sequential memory, and ring counters. The ope

0 views • 10 slides

Understanding BUS Systems in Computer Architecture

This article explores the concept of BUS systems in computer architecture, focusing on the efficient transfer of information between registers using a common bus structure. It delves into the implementation of bus systems for multiple-register configurations, such as a bus system for four registers

0 views • 24 slides

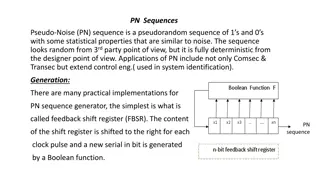

Understanding Pseudo-Noise Sequences and Applications

Pseudo-Noise (PN) sequences are deterministic yet appear random, with applications in various fields such as communication security, control engineering, and system identification. Generated using shift registers, they exhibit statistical properties akin to noise. Linear and nonlinear feedback shift

1 views • 19 slides

Director ID Trust Deed Webinar - Modernising Business Registers Program Update

Director ID Trust Deed webinar on 7th December 2021 introduces the Director Identification Number (director ID) initiative to enhance trust and transparency in business registrations. The program aims to modernize business registers, streamline registration processes, and improve data accuracy, maki

0 views • 21 slides

Understanding the 8051 Microcontroller: Features, Registers, and Applications

A detailed overview of the 8051 microcontroller including its introduction, features, and registers. Explore how the 8051 is useful for small computing tasks, control applications, and its low power consumption. Learn about the various registers in the 8051 such as the accumulator, program counter,

0 views • 18 slides

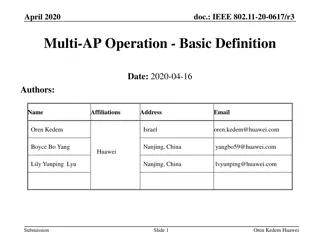

Understanding Multi-AP Operation in IEEE 802.11-20-0617/r3

Explore the basic definitions and key features of Multi-AP operation in the IEEE 802.11 standard. Learn about Multi-AP Candidate Set (M-AP-CS) and Multi-AP Operation Set (M-AP-OS) along with their participants and formation. Delve into the concepts of Coordinator AP, Coordinated AP(s), and reliable

0 views • 19 slides

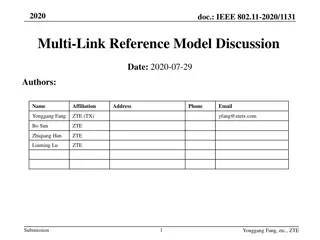

IEEE 802.11-2020 Multi-Link Reference Model Discussion

This contribution discusses the reference model to support multi-link operation in IEEE 802.11be and proposes architecture reference models to support multi-link devices. It covers aspects such as baseline architecture reference models, logical entities in different layers, Multi-Link Device (MLD) f

1 views • 19 slides

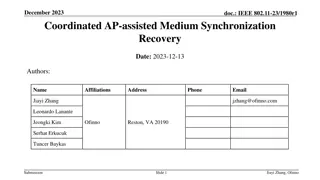

IEEE 802.11-23/1980r1 Coordinated AP-assisted Medium Synchronization Recovery

This document from December 2023 discusses medium synchronization recovery leveraging multi-AP coordination for multi-link devices. It covers features such as Multi-link device (MLD), Multi-link operation (MLO), and Ultra High Reliability (UHR) capability defined in P802.11bn for improvements in rat

0 views • 8 slides

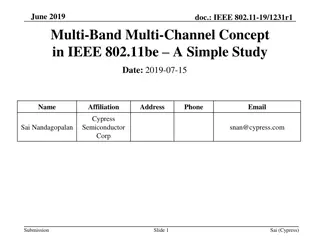

Understanding Multi-Band Multi-Channel Concept in IEEE 802.11be

Exploring the benefits of Multi-Band Multi-Channel (MBMC) operation in IEEE 802.11be, this study delves into the efficient use of spectrum, increased data rates, and network load balancing. It also discusses the envisioned usage models and compares Single Band Operation with Multi-Band Operation, hi

1 views • 20 slides

The Case for Population Registers: Key Requirements and Implementation Status Across Africa

Population registers play a crucial role in providing robust and timely population data, especially in the current era emphasizing rigorous measurement and monitoring of human development. Implementing e-government platforms and facing challenges like the Covid-19 pandemic have highlighted the impor

0 views • 18 slides

Challenges in Transition from Primary to Secondary School: Corpus Design

The linguistic challenges in transitioning from primary to secondary school in England are explored in this project. The focus is on academic school language and the barriers students face in understanding the curriculum, particularly at the start of Key Stage 3. The differing registers of academic

0 views • 28 slides

Overview of 8086 Assembly Language Arithmetic Operations

The 8086 assembly language provides instructions for arithmetic operations such as addition, subtraction, and comparison. These operations are essential for manipulating data in memory and registers. The instructions support various operand types, including registers, memory locations, and immediate

0 views • 24 slides

Understanding Quality Dimensions in Statistical Business Registers

Quality in statistical business registers encompasses dimensions such as relevance, accuracy, timeliness, accessibility, comparability, and coherence. The United Nations provides guidance on quality frameworks for official statistics, emphasizing the importance of tailoring quality assurance policie

0 views • 28 slides

Understanding Shift Registers: Introduction and Classification

Explore the world of shift registers, including buffer registers, and different modes of operation like serial in/serial out, serial in/parallel out, parallel in/serial out, and parallel in/parallel out. Learn about the construction, operation, and classification of registers in digital systems.

1 views • 24 slides

Understanding Shift Registers in Sequential Logic Circuits

Shift registers are sequential logic circuits used for storing digital data. They consist of interconnected flip-flops that shift data in a controlled manner. This article explores different types of shift registers such as Serial In - Serial Out, Serial In - Parallel Out, Parallel In - Serial Out,

2 views • 9 slides

Digital Logic Design Lecture on Registers and Counters

In this lecture, we covered topics on Registers and Counters in digital logic design. Registers are used to hold information within a digital system, while Counters are utilized to produce specified output pattern sequences. Different types of registers such as shift registers were discussed along w

0 views • 25 slides

Understanding Branching and Condition Codes in Computer Architecture

Explore the intricacies of branching statements, if-else statements, condition codes, explicit compare and branch, implicit condition codes, and the use of condition registers in computer architecture. Delve into MIPS architecture's utilization of both implicit and condition registers for efficient

0 views • 16 slides

Understanding x86-64 Procedures and Data Structures

This content provides insights into x86-64 programming, covering topics such as procedures, integer registers, stack frames, locals in the red zone, interesting features of stack frames, arrays, multi-dimensional structures, and more. It dives into the usage conventions of integer registers, the all

0 views • 44 slides

Virtual Carrier Sense in Multi-Link Networks

This document discusses the implementation and advantages of virtual carrier sense in multi-link networks under the IEEE 802.11 standard. It explores the operation of multi-link setups, asynchronous communication benefits, and the necessity of multiple contention channels. The concept of NAV (Networ

2 views • 11 slides

Enhancing Maternal Health Data Recording with Dakshata Initiative

Utilizing data-driven approaches through Dakshata initiative to improve data recording related to childbirth by implementing standardized registers, training staff, and conducting regular reviews at healthcare facilities. This includes dashboard monitoring, establishment of best practices, and sugge

0 views • 6 slides

Nordic Prescription Registers in Iceland: Overview and Coverage

The Nordic Prescription Registers in Iceland provide detailed data on prescription drug dispensing, covering variables such as drug user information, dispensing details, prescriber data, pharmacy information, and more. The database includes information on all reimbursed and non-reimbursed prescripti

0 views • 11 slides

Research Department on Prescription Registers in Finland

Research Department in Finland, led by Leena K. Saastamoinen from The Social Insurance Institution (Kela), focuses on prescription registers and essential demographics, including the size of the population. The department collaborates with relevant institutions and is located in Helsinki. They manag

0 views • 15 slides

Understanding SIMD for High-Performance Software Development

SIMD (Single Instruction Multiple Data) hardware support utilizes vector registers for high-performance computing. Vector instructions operate on multiple data elements simultaneously, offering scalability and efficient processing strategies. The use of wide vector registers enhances arithmetic oper

0 views • 41 slides

Performance Aspects of Multi-link Operations in IEEE 802.11-19/1291r0

This document explores the performance aspects, benefits, and assumptions of multi-link operations in IEEE 802.11-19/1291r0. It discusses the motivation for multi-link operation in new wireless devices, potential throughput gains, classification of multi-link capabilities, and operation modes. The s

0 views • 30 slides

Understanding Descriptor Tables and Registers in Computer Systems

Descriptor tables in computer systems group segment descriptors together for efficient memory management. They consist of Global Descriptor Table (GDT), Local Descriptor Table (LDT), and Interrupt Descriptor Table (IDT). The Global Descriptor Table (GDT) is a crucial table that is shared by all prog

0 views • 18 slides

Introduction to Y86 Instruction Set Architecture

Y86 Instruction Set Architecture is a simplified pseudo-language based on x86 (IA-32) architecture. It involves implementing the Fetch-Decode-Execute cycle, where instructions are fetched from memory, decoded, and executed. The Y86 ISA offers a simpler set of instructions and formats compared to x86

0 views • 25 slides

Multi-Stage, Multi-Resolution Beamforming Training for IEEE 802.11ay

In September 2016, a proposal was introduced to enhance the beamforming training procedures in IEEE 802.11ay for increased efficiency and MIMO support. The proposal suggests a multi-stage, multi-resolution beamforming training framework to improve efficiency in scenarios with high-resolution beams a

0 views • 11 slides

Efficient Snapshot Implementations in Distributed Systems

This content discusses various snapshot implementations in distributed systems, focusing on achieving faster and sub-linear snapshot complexity. It covers topics such as multi-writer registers, tree structures, polylogarithmic snapshots, and the challenges of ensuring consistency across processes. T

0 views • 16 slides

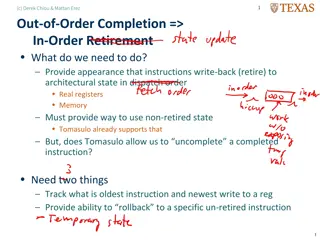

Enhancing Out-of-Order Completion with In-Order Retirement

To improve performance, instructions are retired in dispatch order rather than completion order. Introduce appearance changes in architectural state, track oldest and newest instructions, and allow rollback to un-retired instructions. Implement reorder buffers, separate rename registers, and utilize

0 views • 5 slides

Evolution of Register-Based Census in Sweden

The development of a register-based census in Sweden, initiated with Census 2011, has transitioned from a mix of registers and questionnaires to a fully register-based system. Motivations include cost reduction and efficient data collection for yearly statistics on households, housing, and dwellings

0 views • 10 slides

Understanding MIPS Functions and Calling Conventions

MIPS functions in assembly language are called using the 'jal' instruction, passing arguments in specific registers. Functions must end with 'jr $ra' and have explicit declarations. MIPS functions are stored separately from the main function in memory. The 'jal' instruction jumps to a specified addr

0 views • 18 slides