Enhancing Low Latency Channel Access in Legacy IEEE 802.11 Networks

This document discusses the impact of introducing a Low Latency (LL) channel access mechanism in legacy IEEE 802.11 networks. It addresses the use of High Priority EDCA (HiP EDCA) mechanisms, proposing solutions for improving tail latency in both isolated BSS and multi-BSS scenarios. Additionally, it explores the effects on legacy devices when Unique DS signals are utilized, along with considerations for prioritized access and contention parameters. The research aims to optimize performance without compromising on legacy compatibility.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

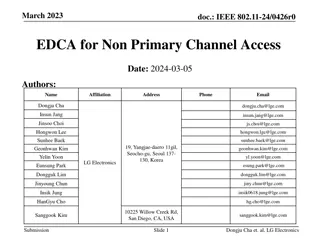

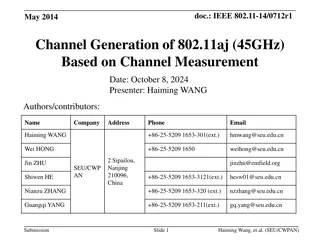

March 2024 doc.: IEEE 802.11-24/0467r0 Low latency channel access Legacy impact Date: 2024-03-06 Authors: Name Affiliations Address Phone email Dmitry Akhmetov Intel Laurent Cariou Intel Dibakar Das Intel Submission Slide 1 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 Recap from 11-23/2126r0: problem High Priority EDCA (HiP EDCA) mechanism based on transmission of a dedicated signal prior to general EDCA contention allow to improve tail latency : 90-95-99th percentiles in both isolated BSS case and multi-BSS setup In situations with and without hidden nodes The repetition of DS signal (i.e. an AP reply with same DS signal) has limited affect on tail latency improvement In terms of design, it is better to have Unique DS signal rather than Common one, i.e. DS signal to be specific to a BSS Rules to send DS signal need to be discussed Frequency of transmission AIFSN boundary for transmission Submission Slide 2 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 Recap from 11-23/1065r0: solution Proposal would be to isolate STAs with prioritized access from the rest of the STAs at the beginning of a contention period Achieve this by allowing these STAs to transmit a Defer Signal at the beginning of a contention period to force all STAs that are not sending the Defer Signal to have CCA busy and not participate in the contention period If multiple of these STAs have prioritized access, they will transmit the same Defer Signal at the same time with the same result on other STAs (CCA busy) And then to allow for a contention only between the STAs with prioritized access Only STAs that have sent a Defer Signal can participate in this immediately following contention More degrees of freedom for the contention parameters setting to avoid collisions without loosing priority don t necessarily need to be too aggressive in order to scale to a larger number of STAs while ensuring low collision rates (contrary to AC_VO) Example: A device with the traffic in AC_VO use legacy EDCA to transmit data. Device is eligible to send DS signal if it experience a failure after using legacy EDCA and doubled its contention window After successfully attempting transmission using DS STA fall back to normal EDCA operations Submission Slide 3 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 New material: Impact on legacy devices What is the effect on legacy devices when UHR device use DS If in a BSS set of STAs is using DS for LL frame transmission and other don t What if one BSS use DS and others don t A mix of above Submission Slide 4 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 Simulation configuration 80meters Enterprise-like layout 1, 2 or 3 BSSes with variable number of STAs: 5,6,..,15, 16 Out of which 2, 3 or 4 are ULL STAs Other STA has bidirectional full buffer BE traffic. 2 4 5 7 9 10 12 14 15 17 19 20 22 24 25 27 29 30 32 34 35 37 39 40 42 44 45 47 49 50 52 54 55 57 59 60 62 64 65 67 69 70 72 74 75 77 79 2 1 2 5 6 4 3 4 7 8 7 1 2 3 4 5 6 7 5 7 9 10 13 14 9 11 12 15 16 10 1 2 5 6 12 3 4 7 8 14 3 4 5 6 7 6 1 2 15 9 10 13 14 17 11 12 15 16 19 20 1 2 5 6 22 3 4 7 8 24 6 7 5 1 2 3 4 5 25 9 10 13 14 27 11 12 15 16 29 30 1 2 5 6 32 3 4 7 8 34 80meters 1 2 3 4 5 4 6 7 4 35 9 10 13 14 37 11 12 15 16 39 # STAs # of VO STAs % of VO STA 5 2 40 6 2 33 7 2 29 8 2 25 9 3 33 10 3 30 11 3 27 12 3 25 13 4 31 14 4 29 15 4 27 16 4 25 40 1 2 5 6 42 3 4 7 8 44 4 5 6 7 3 1 2 3 45 3 9 10 13 14 47 11 12 15 16 49 50 1 2 5 6 52 3 4 7 8 54 7 2 1 2 3 4 5 6 55 2 2 9 10 13 14 57 11 12 15 16 59 60 1 5 6 62 3 4 7 8 64 2 3 4 5 6 7 1 1 65 9 10 13 14 67 5 1 11 12 15 16 69 2x2x20Mhz @ MCS3 TXOP limit = uniform (1.5ms; 5ms) New TXOP limit is selected each time when STA/AP won contention Randomization is only to introduce burstiness and extra randomness into channel occupancy time STA Cw = 15/1023; AP Cw=15/63 TxPower: STA = 17dBm; AP=23dBm Location STAs assigned on a grid across four 4x4 cube islands, AP in the middle of the island Overall area size is 80x80meters 70 1 2 6 72 3 4 7 8 74 5 6 7 0 1 2 3 4 75 9 10 13 14 77 11 12 15 16 79 Submission Slide 5 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 HiP EDCA for AC VO Multi-BSS setup in 80x80 and 20x20 area ULL traffic use AC_VO access category A STA / AP use HiP EDCA after first failure in AC_VO category VO traffic is bi-directional 160 bytes every average 16ms =uniform (10ms, 22ms) BE are legacy with bi-directional full buffer traffic, TXOP = uniform (1.5ms, 5ms) Three cases: 1 BSS case with ULL use AC_VO ULL use DS Half of streams in a BSS use VO and the other one use DS 2 and 4 BSS case All BSSes use AC_VO for ULL All BSSes use DS for ULL Half of BSSes use AC_VO and the other half - DS Half of streams in each BSS use VO and the other one use DS Statistic of interest: ETE delay Submission Slide 6 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 1 BSS case 1 BSS case, 13 STAs in BSS, 4 ULL flows 1 BSS case, 9 STAs in BSS, 3 ULL flows 1 BSS case, 5 STAs in BSS, 2 ULL flows 0.02 0.016 0.01 0.018 0.009 0.014 0.016 0.008 0.012 0.014 0.007 VO VO VO 0.01 0.012 0.006 delay,s delay,s delay,s DS DS DS 0.01 0.005 0.008 Half DS Half DS Half DS 0.008 0.004 0.006 0.006 Halfs VO 0.003 Halfs VO Halfs VO 0.004 0.004 0.002 0.002 0.002 0.001 0 0 0 mean 90 95 98 99 mean 90 95 98 99 mean 90 95 98 99 1 BSS case, 16 STAs in BSS, 4 ULL flows 1 BSS case, 8 STAs in BSS, 2 ULL flows 1 BSS case, 12 STAs in BSS, 3 ULL flows 0.018 0.014 0.02 0.018 0.016 0.012 0.016 0.014 0.01 0.014 0.012 VO VO VO 0.012 delay,s 0.008 0.01 delay,s delay, s DS DS DS 0.01 0.008 0.006 Half DS Half DS Half DS 0.008 0.006 Halfs VO 0.006 Halfs VO Halfs VO 0.004 0.004 0.004 0.002 0.002 0.002 0 0 0 mean 90 95 98 99 mean 90 95 98 99 mean 90 95 98 99 VO all ULL use legacy EDCA Half VO half of ULL use VO DS all ULL use DS Half DS half of ULL use DS Submission Slide 7 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 2 BSS case 2 BSS case, 9 STAs in BSS, 6 ULL flows 2 BSS case, 5 STAs in BSS, 4 ULL flows 2 BSS case, 13 STAs in BSS, 8 ULL flows 0.025 0.016 0.025 0.014 VO VO VO 0.02 0.02 0.012 DS DS DS 0.01 0.015 0.015 delay,s delay,s delay,s BSS DS BSS DS BSS DS 0.008 0.01 0.01 BSS VO BSS VO 0.006 BSS VO 0.004 Half DS Half DS Half DS 0.005 0.005 0.002 Halfs VO Halfs VO Halfs VO 0 0 0 mean 90 95 98 99 mean 90 95 98 99 mean 90 95 98 99 2 BSS case, 16 STAs in BSS, 8 ULL flows 2 BSS case, 12 STAs in BSS, 6 ULL flows 2 BSS case, 8 STAs in BSS, 4 ULL flows 0.03 0.025 0.02 0.018 VO 0.025 VO VO 0.02 0.016 DS 0.014 DS DS 0.02 delay,s 0.015 0.012 delay,s delay,s BSS DS BSS DS BSS DS 0.015 0.01 BSS VO 0.01 0.008 BSS VO BSS VO 0.01 0.006 Half DS Half DS Half DS 0.005 0.004 0.005 0.002 Halfs VO Halfs VO Halfs VO 0 0 0 mean 90 95 98 99 mean 90 95 98 99 mean 90 95 98 99 VO all ULL use legacy EDCA Half VO half of ULL use VO BSS VO half of BSS use VO DS all ULL use DS Half DS half of ULL use DS BSS DS half of BSS use DS Submission Slide 8 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 4 BSS case 4 BSS case, 13 STAs in BSS, 16 ULL flows 4 BSS case, 5 STAs in BSS, 8 ULL flows 4 BSS case, 9 STAs in BSS, 12 ULL flows 0.03 0.025 0.025 VO 0.025 VO 0.02 VO 0.02 DS 0.02 DS DS delay,s 0.015 0.015 delay,s delay,s BSS DS BSS DS BSS DS 0.015 BSS VO BSS VO 0.01 0.01 BSS VO 0.01 Half DS Half DS Half DS Halfs VO 0.005 0.005 0.005 Halfs VO Halfs VO 0 0 0 mean 90 95 98 99 mean 90 95 98 99 mean 90 95 98 99 4 BSS case, 16 STAs in BSS, 16 ULL flows 4 BSS case, 8 STAs in BSS, 8 ULL flows 4 BSS case, 12 STAs in BSS, 12 ULL flows 0.035 0.025 0.03 0.03 VO VO VO 0.025 0.02 0.025 DS DS DS 0.02 delay,s 0.015 0.02 delay,s delay,s BSS DS BSS DS BSS DS 0.015 0.015 BSS VO 0.01 BSS VO BSS VO 0.01 0.01 Half DS Half DS Half DS 0.005 0.005 0.005 Halfs VO Halfs VO Halfs VO 0 0 0 mean 90 95 98 99 mean 90 95 98 99 mean 90 95 98 99 VO all ULL use legacy EDCA Half VO half of ULL use VO BSS VO half of BSS use VO DS all ULL use DS Half DS half of ULL use DS BSS DS half of BSS use DS Submission Slide 9 Dmitry Akhmetov et. al., Intel

March 2024 doc.: IEEE 802.11-24/0467r0 Conclusion There is no negative impact on LL stream using legacy EDCA mechanism in presence of devices using HiP EDCA mechanism Submission Slide 10 Dmitry Akhmetov et. al., Intel