DarkLight CM TRIUMF May/June 2023 Prototype Scintillator Development Details

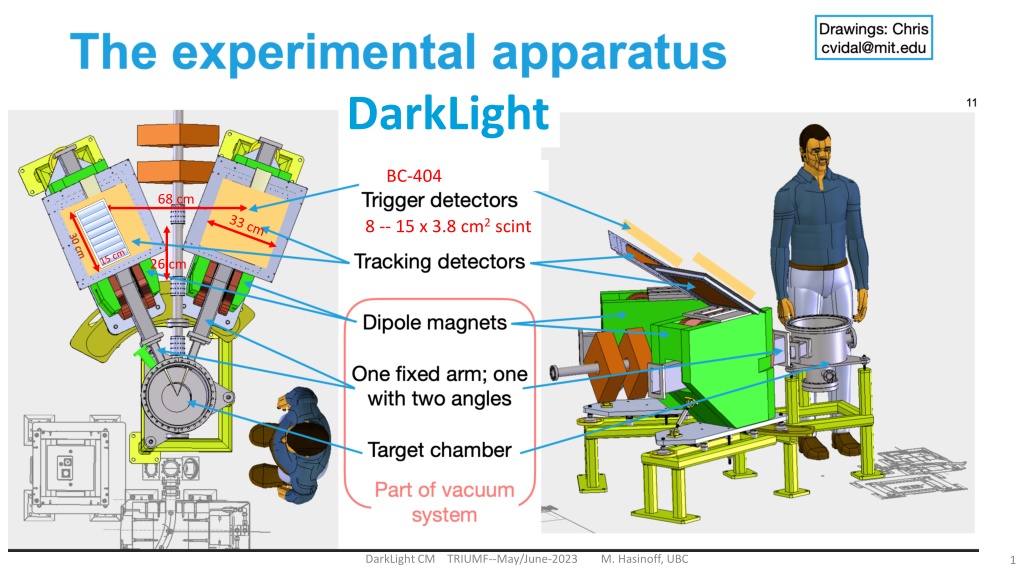

The DarkLight project at TRIUMF in May/June 2023 involves the development of prototype scintillators with specific requirements for triggering, timing adjustments, and readout capabilities. Various images depict different components such as SiPMs, front-end readout cards, and TOF Alpha bars. The project aims to achieve high-resolution electron-positron coincidences and offline time walk corrections. Detailed descriptions and specifications are provided for each component, emphasizing the need for precise timing and triggering mechanisms.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

DarkLight BC-404 68 cm 8 -- 15 x 3.8 cm2 scint 26 cm DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 1

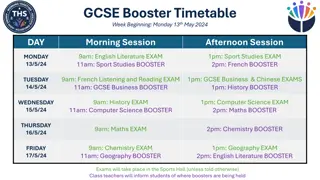

positron (30 kHz) electron (3.6 MHz) 150mm 150mm 8-o 7-o 6-o 5-o 4-o 3-o 2-o 1-o 16-i 15-i 14-i 13-i 12-i 11-i 10-i 9-i 8-i 7-i 6-i 5-i 4-i 3-i 2-i 1-i 16-o 15-o 14-o 13-o 12-o 11-o 10-o 9-o 38mm 38mm 304mm Different FPGA programs required 1. 2. 3. 4. 4. Need to be able to trigger on single counters for calibration. Need to adjust timing for each counter to account for the different path lengths in the spectrometers. Need to form L-R coincident triggers for each bar, then form OR of 8 e- bars, 8 e+ bars, then trigger e- * e+ Need to generate the fast trigger for readout of the GEM tracking chambers within 1 usec (??) For each of the 16 scintillators that have signals above threshold -- make in-out coincidence -- make electron positron coincidence ( want < 200 psec time resolution ) -- output LE and TE time for an offline time walk correction DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 2

TOF Alpha bar with #1 DL Prototype Bar ? = 335 4 ???? DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 3

v1b -- 6 SiPM DarkLight Scintillator 38mm wide BC-404 SiPM spacing at 7.50mm to match the existing frontend readout board designed for 4 SiPMs on 30mm scintillator -- not tested DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 4

v2 -- 6 SiPM DarkLight Scintillator 38mm wide BC-404 DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 5

v2-- Prototype Scintillator May 2023 38 mm wide with 6 SiPMs at each end One Electronic card holds 2 scintillators and 12 SiPMs DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 6

NEW v2 front end readout card (top side) holds 12 SiPMs/2 scintillators SUM(6) fast amp discriminator FPGA will check e+ e- coincidence FPGA will readout LE and TE time Preamp, Sum Amp, Discriminator J3 = Pulser-in J7 = TS1 out J2 = Logic Out Next Stages measure time resolution (L-R) measure time resolution -- 2 bars design power dist n board design test pulse dist n system develop trigger FPGA system J4 = +/-5V J5 = +/-5V J1 = BIAS 55 V J6 = TS2 out DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 7

NEW v2 front end readout card (bottom side) SiPMs--7-12 SiPMs--1-6 DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 8

Square wave Test Input pulse DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 9

SiPM Dark Noise @ 8V overvoltage RT= 924 ps DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 10

2 1 1 2 1 2 2 1 GND NetC2-1_1 NetC2-1_1 NetC1-1_1 NetC1-1_1 +5V0 GND NetC5-1_1 1 2 1 1 2 3 GND GND NetC2-1_1 NetC1-1_1 GND 2 1 NetC1-1_1 3 Vbias NetC5-1_1 NetQ2-1_3 1 2 1 2 4 5 2 1 2 NetQ2-1_3 NetC2-1_1 NetC4-1_1 PAout1 GND GND NetQ2-1_2 Fid 1 2 NetC8-1_1 NetQ2-1_2 GND NetC8-1_1 1 2 2 2 1 2 1 2 1 NetQ2-1_3 NetQ1-1_1 NetQ2-1_2 GND NetC6-1_1 -5V0 NetQ1-1_1 NetC4-1_1 NetC4-1_1 MH2 GND 2 1 1 2 2 1 2 3 1 1 1 T1 1 1 NetC8-1_2 NetC8-1_2 2 1 2 GND Vtest Vtest NetC8-1_1 GND +3V3 +5V0 +3V3 +5V0 +3V3 NetC6-1_1 NetC6-1_1 NetC6-1_1 NetC6-1_1 GND 1 NetJ3_1 MCX output connectors MH2 GND 2 2 4 2 1 1 2 1 2 GND GND GND 2 1 GND NetC2-2_1 NetC2-2_1 NetC1-2_1 NetC1-2_1 +5V0 GND NetC5-2_1 3 2 1 2 1 1 2 3 GND GND GND Fid GND NetC2-2_1 NetC1-2_1 GND MH1 GND 2 1 NetC1-2_1 3 Vbias NetC5-2_1 NetQ2-2_3 1 2 1 2 2 1 2 NetQ2-2_3 NetC2-2_1 NetC4-2_1 PAout2 Fid NetQ2-2_2 1 2 NetC8-2_1 NetQ2-2_2 GND NetC8-2_1 1 2 2 2 1 2 1 2 1 NetQ2-2_3 NetQ1-2_1 NetQ2-2_2 GND NetC6-2_1 -5V0 NetQ1-2_1 NetC4-2_1 NetC4-2_1 1 2 2 1 2 1 4 5 T1 2 1 GND CMPA_P CMPA_N GND 1 1 2 NetC8-2_2 NetC8-2_2 GND GND 2 1 2 +5V0 1 2 1 Vtest NetC8-2_1 NetC6-2_1 NetC6-2_1 GND NetC6-2_1 NetC6-2_1 GND GND +5V0 +V 2 1 1 2 1 GND +3V3 +3V3 GND GND 2 1 2 12 CMPA_P 11 CMPA_N 10 9 1 2 2 1 +3V3 2 1 1 2 1 2 +3V3 1 2 -5V0 2 1 +3V3 +3V3 +5V0 GND GND +V GND NetC2-3_1 NetC2-3_1 NetC1-3_1 NetC1-3_1 +5V0 TPout1 -5V0 13 -5V0 GND NetC5-3_1 8 7 6 1 2 1 1 2 1 14 3 1 2 GND GND NetC2-3_1 NetC1-3_1 GND NetR48-1_1 NetR52-1_2 NetR48-1_1 NetR49-1_1 5 +5V0 4 NetC43-1_1 Sout1 VTH2 NetC42-1_1 2 1 17 15 GND NetC1-3_1 3 2 -5V0 NetR52-1_2 Vbias NetC5-3_1 NetQ2-3_3 +5V0 16 1 8 7 6 5 1 2 1 2 1 2 1 1 +5V0 1 2 +5V0 +V 1 NetQ2-3_3 NetC2-3_1 NetC4-3_1 PAout3 +V 3 2 2 NetQ2-3_2 1 2 +5V0 NetR49-1_1 1 2 3 NetC8-3_1 NetQ2-3_2 +5V0 1 1 2 9 GND GND +5V0 +V GND PWREN 1 GND NetC8-3_1 3 1 2 2 2 +5V0 GND PAout1 GND 1 2 1 2 1 NetR29_1 NetR29_1 NetQ2-3_3 NetQ1-3_1 NetQ2-3_2 GND 2 4 NetC6-3_1 -5V0 NetC4-3_1 NetQ1-3_1 NetC4-3_1 1 1 2 2 2 1 2 PWREN NetC26_2 2 1 1 1 1 NetC42-1_1 NetC43-1_1 GND GND 2 2 NetC8-3_2 NetC8-3_2 GND 2 1 2 Vtest NetC8-3_1 PAout1 NetC6-3_1 NetC6-3_1 NetR29_1 NetC26_2 NetC6-3_1 NetC6-3_1 GND 2 GND 2 1 2 2 2 S-in-1 GND PAout2 GND GND 1 1 GND GND 1 2 2 1 1 2 1 2 PAout2 S-in-1 2 1 GND NetC2-4_1 NetC2-4_1 NetC1-4_1 NetC1-4_1 +5V0 GND NetC5-4_1 1 2 1 2 2 1 1 2 1 2 1 1 2 GND PAout3 PAout3 S-in-1 S-in-1 NetC17-1_1 NetR21-1_1 GND 3 1 GND GND NetC2-4_1 NetC1-4_1 GND 2 1 NetC1-4_1 GND 3 2 1 1 2 1 2 Vbias NetC5-4_1 1 NetQ2-4_3 -5V0 GND GND PAout4 PAout4 S-in-1 1 2 1 2 4 3 2 GND 1 2 NetQ2-4_3 NetC2-4_1 NetC4-4_1 PAout4 S-in-1 NetR21-1_1 NetQ2-4_2 1 2 1 2 NetC8-4_1 NetQ2-4_2 2 GND NetC8-4_1 PAout5 S-in-1 1 2 5 2 2 2 1 2 1 2 2 1 1 2 1 2 -5V0 NetQ2-4_3 NetQ1-4_1 NetQ2-4_2 GND +5V0 -5V0 CMPA_P CMPA_N NetC6-4_1 -5V0 NetQ1-4_1 NetC4-4_1 NetC4-4_1 -5V0 GND -5V0 1 2 2 2 1 2 1 6 1 GND PAout5 1 1 S-in-1 NetC8-4_2 NetC8-4_2 2 1 2 Vtest NetC8-4_1 1 2 +5V0 NetC17-1_1 1 NetC6-4_1 NetC6-4_1 3 2 1 NetC6-4_1 NetC6-4_1 GND 1 NetR15-1_1 TPout1 1 1 2 NetR15-1_1 Sout1 -5V0 NetR15-1_1 Sout1 PAout6 NetC17-1_1 Sout1 1 2 3 4 +5V0 GND 2 1 2 CMPB_P CMPB_N 2 NetR14-1_2 2 1 1 2 1 2 GND PAout6 GND 2 1 GND NetC2-5_1 NetC2-5_1 NetC1-5_1 NetC1-5_1 +5V0 GND NetC5-5_1 1 2 4 5 6 1 2 1 2 1 1 2 +5V0 GND NetR14-1_2 +5V0 +5V0 3 GND NetR14-1_2 GND GND NetC2-5_1 NetC1-5_1 GND 2 1 NetC1-5_1 3 T1 GND Fid Vbias NetC5-5_1 NetQ2-5_3 5 6 1 2 1 2 2 1 2 GND GND 1 2 MH1 GND NetQ2-5_3 NetC2-5_1 NetC4-5_1 PAout5 GND +5V0 NetQ2-5_2 1 2 NetC8-5_1 NetQ2-5_2 GND NetC8-5_1 1 2 2 2 1 2 1 1 2 NetQ2-5_3 NetQ1-5_1 NetQ2-5_2 GND 4 3 NetC6-5_1 -5V0 NetQ1-5_1 NetC4-5_1 NetC4-5_1 2 1 2 1 GND A0 2 1 GND +5V0 1 1 NetC8-5_2 NetC8-5_2 2 1 2 Vtest NetC8-5_1 NetC6-5_1 NetC6-5_1 NetC6-5_1 NetC6-5_1 GND 2 2 -5V0 +5V0 2 1 GND A1 2 1 1 2 1 2 2 1 GND NetC2-6_1 NetC2-6_1 NetC1-6_1 NetC1-6_1 +5V0 T1 GND NetC5-6_1 1 2 1 2 VTH2 VTH2 NetR42_2 NetR42_2 DAC-B 1 2 1 1 2 1 1 3 GND GND NetC2-6_1 NetC1-6_1 GND Fid 2 1 T1 Vref GND GND NetC1-6_1 3 Vbias NetC5-6_1 NetQ2-6_3 1 2 1 2 2 1 2 2 1 1 2 NetQ2-6_3 NetC2-6_1 NetC4-6_1 PAout6 NetR46_1 NetR46_1 NetQ2-6_2 +3V3 A1 1 2 8 7 6 5 NetC8-6_1 NetQ2-6_2 GND NetC8-6_1 +5V0 VTH2 NetR42_2 NetR46_1 1 2 2 2 1 2 1 2 1 2 1 16 NetQ2-6_3 NetQ1-6_1 NetQ2-6_2 GND 1 2 NetC6-6_1 -5V0 NetQ1-6_1 NetC4-6_1 NetC4-6_1 +5V0 Vref +3V3 2 1 GND DAC-A 2 1 2 15 1 1 NetC8-6_2 NetC8-6_2 2 1 2 Vtest NetC8-6_1 1 2 DAC-B +3V3 NetC6-6_1 NetC6-6_1 NetC6-6_1 NetC6-6_1 GND 1 2 3 14 A1 1 GND Vbias 1 GND +3V3 DAC-A GND 3 1 1 GND 1 4 13 SCL +Vin GND 1 GND GND GND A0 5 12 A0 1 1 6 5 4 MH2 GND +5V0 2 GND GND GND +3V3 SDA 6 11 +5V0 2 DAC-C +3V3 2 2 -5V0 7 10 GND +3V3 RTS 2 2 1 2 3 4 DAC-D NetC27_2 NetC27_2 VTH1 NetR38_2 NetR40_1 -5V0 8 9 2 1 1 2 4 2 2 1 1 2 1 2 SDA GND NetJ3_1 Vtest Vtest NetJ3_1 1 2 3 2 1 -Vin GND GND NetC2-7_1 NetC2-7_1 NetC1-7_1 NetC1-7_1 +5V0 1 NetC27_2 GND SCL GND NetC5-7_1 NetC27_2 2 1 2 1 1 2 1 1 2 2 3 1 SCL +3V3 +3V3 GND GND GND NetC2-7_1 NetC1-7_1 GND 2 1 2 1 1 1 2 GND NetC1-7_1 GND 3 2 NetR40_1 GND Vbias NetC5-7_1 NetR38_2 Fid VTH1 NetR38_2 NetQ2-7_3 Vbias 1 2 1 2 2 1 2 1 2 NetQ2-7_3 NetC2-7_1 NetC4-7_1 PAout7 SDA +3V3 NetQ2-7_2 1 2 1 2 NetC8-7_1 NetQ2-7_2 T1 2 1 2 NetR40_1 DAC-C GND NetC8-7_1 1 2 2 2 Vbias T1 DAC-D 1 2 1 2 1 Vbias +HV NetQ2-7_3 NetQ1-7_1 NetQ2-7_2 GND VTH1 NetC6-7_1 -5V0 NetQ1-7_1 NetC4-7_1 NetC4-7_1 2 1 2 1 1 1 NetC8-7_2 NetC8-7_2 2 1 2 Vtest NetC8-7_1 NetC6-7_1 NetC6-7_1 NetC6-7_1 NetC6-7_1 GND T1 GND 1 +V 2 1 1 2 1 2 2 1 GND NetC2-8_1 NetC2-8_1 NetC1-8_1 NetC1-8_1 +5V0 Fid GND NetC5-8_1 1 2 1 1 2 3 GND GND NetC2-8_1 NetC1-8_1 GND 2 1 MH1 GND NetC1-8_1 3 1 2 2 1 Vbias NetC5-8_1 NetQ2-8_3 3 1 GND CMPB_P CMPB_N GND 2 1 2 1 2 2 2 1 +Vin GND 1 2 +Vin NetQ2-8_3 NetC2-8_1 NetC4-8_1 PAout8 GND NetQ2-8_2 GND 1 2 NetC8-8_1 NetQ2-8_2 2 1 1 2 1 GND NetC8-8_1 1 2 2 2 1 2 1 2 1 GND +3V3 +3V3 GND GND NetQ2-8_3 NetQ1-8_1 NetQ2-8_2 GND NetC6-8_1 -5V0 NetC4-8_1 NetQ1-8_1 NetC4-8_1 2 1 2 2 1 1 1 1 2 NetC8-8_2 NetC8-8_2 12 CMPB_P 11 CMPB_N 10 9 2 1 2 +3V3 Vtest NetC8-8_1 +3V3 2 NetC6-8_1 NetC6-8_1 -5V0 +3V3 +3V3 NetC6-8_1 NetC6-8_1 GND -5V0 13 -5V0 2 4 2 8 7 1 -Vin 14 -Vin GND 1 2 NetR48-2_1 NetR52-2_2 NetR48-2_1 6 NetR49-2_1 5 +5V0 4 NetC43-2_1 Sout2 VTH1 NetC42-2_1 17 15 GND -5V0 NetR52-2_2 2 1 1 2 1 2 16 2 1 GND NetC2-9_1 NetC2-9_1 NetC1-9_1 NetC1-9_1 +5V0 1 1 +5V0 1 GND NetC5-9_1 +5V0 NetR49-2_1 1 2 3 +5V0 1 1 2 1 2 1 1 2 3 +5V0 GND PAout7 GND GND NetC2-9_1 NetC1-9_1 GND 2 1 NetC1-9_1 3 1 -V Vbias NetC5-9_1 1 1 2 2 2 NetQ2-9_3 1 1 2 1 2 NetC42-2_1 NetC43-2_1 GND GND GND 2 PAout7 1 2 NetQ2-9_3 NetC2-9_1 NetC4-9_1 PAout9 NetQ2-9_2 2 1 2 NetC8-9_1 NetQ2-9_2 GND 2 1 2 GND NetC8-9_1 1 2 2 2 2 2 1 2 1 2 1 S-in-2 GND PAout8 NetQ2-9_3 NetQ1-9_1 NetQ2-9_2 GND GND GND NetC6-9_1 -5V0 NetQ1-9_1 NetC4-9_1 NetC4-9_1 2 1 2 1 1 2 1 1 NetC8-9_2 NetC8-9_2 2 1 2 Vtest NetC8-9_1 PAout8 S-in-2 1 -V NetC6-9_1 NetC6-9_1 NetC6-9_1 NetC6-9_1 GND 2 1 -V 2 GND 1 2 1 2 2 1 1 2 7 8 GND GND PAout9 PAout9 S-in-2 S-in-2 NetC17-2_1 NetR21-2_1 GND 1 +HV GND GND 2 1 1 2 1 2 2 2 1 1 2 1 2 1 2 -V -5V0 GND GND PAout10 PAout10 S-in-2 1 2 1 4 3 -5V0 NetC2-10_1 GND NetC2-10_1 NetC1-10_1 NetC1-10_1 +5V0 GND 1 -V 10 -5V0 9 -5V0 8 GND 7 6 PWREN -5V0 GND NetC5-10_1 S-in-2 NetR21-2_1 1 2 2 -V 1 5 6 2 1 1 2 2 PAout11 S-in-2 5 2 T1 -5V0 3 2 1 GND RTS PWREN NetC2-10_1 GND NetC1-10_1 GND 2 1 2 1 -5V0 3 11 -V +5V0 -5V0 NetC1-10_1 3 -5V0 GND -5V0 NetR27_1 Vbias NetC5-10_1 NetR27_1 1 2 2 4 -V NetQ2-10_3 1 2 1 2 6 1 GND PAout11 S-in-2 2 NetC44_2 1 2 5 1 2 2 1 NetQ2-10_3 NetC2-10_1 NetC4-10_1 PAout10 +5V0 NetC17-2_1 1 3 2 1 NetQ2-10_2 1 2 1 NetC8-10_1 NetQ2-10_2 NetR24_2 NetR15-2_1 TPout2 NetC44_2 GND 1 1 2 NetR15-2_1 Sout2 -5V0 NetR15-2_1 3 4 GND NetC8-10_1 1 2 Sout2 2 2 PAout12 NetC17-2_1 Sout2 1 2 1 1 2 SDA GND 1 2 NetQ2-10_3 NetQ1-10_1 NetQ2-10_2 GND NetC6-10_1 -5V0 NetQ1-10_1 NetC4-10_1 NetC4-10_1 +5V0 GND 2 1 1 2 2 1 2 2 1 1 2 1 1 2 NetC8-10_2 NetC8-10_2 GND NetR24_2 NetC44_2 GND 2 1 2 NetR14-2_2 Vtest NetC8-10_1 GND PAout12 NetC6-10_1 NetC6-10_1 GND NetC6-10_1 NetC6-10_1 GND 1 2 1 2 4 5 6 1 2 SCL GND +5V0 GND NetR14-2_2 +5V0 +5V0 GND NetR14-2_2 Fid Fid 2 1 1 2 1 2 2 1 2 1 NetC2-11_1 GND NetC2-11_1 NetC1-11_1 NetC1-11_1 +5V0 GND NetC5-11_1 GND +5V0 1 2 1 1 2 3 GND NetC2-11_1 GND NetC1-11_1 GND 2 1 NetC1-11_1 3 2 1 Vbias NetC5-11_1 NetQ2-11_3 GND +5V0 1 2 1 2 2 1 2 NetQ2-11_3 NetC2-11_1 NetC4-11_1 PAout11 NetQ2-11_2 MH1 GND 1 2 NetC8-11_1 NetQ2-11_2 GND NetC8-11_1 1 2 2 2 4 5 1 2 1 2 1 NetQ2-11_3 NetQ1-11_1 NetQ2-11_2 GND GND GND NetC6-11_1 -5V0 NetQ1-11_1 NetC4-11_1 NetC4-11_1 2 1 2 1 1 1 NetC8-11_2 NetC8-11_2 2 1 2 Vtest NetC8-11_1 NetC6-11_1 NetC6-11_1 NetC6-11_1 NetC6-11_1 GND MH2 GND 1 TPout2 2 1 1 2 1 2 2 1 NetC2-12_1 GND NetC2-12_1 NetC1-12_1 NetC1-12_1 +5V0 MH2 GND GND NetC5-12_1 1 2 1 1 2 3 GND NetC2-12_1 GND NetC1-12_1 GND 2 1 NetC1-12_1 3 Vbias NetC5-12_1 Fid 3 2 NetQ2-12_3 1 2 1 2 GND GND 2 1 2 NetQ2-12_3 NetC2-12_1 NetC4-12_1 PAout12 NetQ2-12_2 1 2 NetC8-12_1 NetQ2-12_2 GND NetC8-12_1 1 2 2 2 1 2 1 2 1 NetQ2-12_3 NetQ1-12_1 NetQ2-12_2 GND NetC6-12_1 -5V0 NetQ1-12_1 NetC4-12_1 NetC4-12_1 2 1 1 2 2 1 1 1 NetC8-12_2 NetC8-12_2 2 1 2 GND Vtest Vtest NetC8-12_1 NetC6-12_1 NetC6-12_1 NetC6-12_1 NetC6-12_1 GND DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 11

1 2 3 4 v2 Schematic May 2023 FB1 +5V0 -5V0 1 2 FB2 J1A J1B -V -5V0 1 2 GND -V DNF 1 2 SCL 1 2 C18 C19 DNF GND GND R24 10V 47u 10V 47u C20 C21 C22 3 4 SDA 3 4 U3 GND 4.7u 1k 1 2 5 4 GND GND +V 4.7u 4.7u IN IN IN IMONN IMONP A A 5 6 RTS 5 6 GND +5V0 PWREN R26 R25 -V U4 11 2k 2k 7 8 7 8 8 1 2 9 10 GND VIN VOUT VOUT R27 OUT OUT -5V0 U5 RTS 7 R29 6 PWREN 100k +5V0 MCP1754ST-3302E/MB +3V3 VIN 24.9k SHDN R28 5k 0805 +HV 0R +3V3 1 3 C23 DF11-8DP-2DS(24) VIN VOUT GND 5 3 3 EN SENSE ILIM 4.7u C24 C25 PWREN GND 4 7 8 +HV 4.7u 4.7u SS SET GND GND R30 2 4 C26 6 DNF LT3090EDD#TRPBF GND GND 1nF 9 C44 R31 C27 GND EP R32 1nF 10k GND 100k ADM7170ACPZ-5.0-R7 GND 0.1u U6 Power estimate Sheet +mA/-mA CMP +130/-70 PREAMP +180/-180 SUM +30/-30 TOP +20/-10 R33 1 6 4 3 SDA SCL GND VIN+ VIN- SDA SCL 1M 0.1% GND R34 S1 DL-Scint-SumAmp.SchDoc 20k 0.1% 5 2 Vbias +3V3 VDD VSS GND PAout1 PAout2 PAout3 PAout4 PAout5 PAout6 MCP3421A3T-E/CH C29 +3V3 S1 S2 CMP1 DL-Scint-Comparator.SchDoc TOTAL = +360/-290mA C28 GND 100V 2u2 GND S3 S4 S5 S6 CMPA_N Sout1 B B Sout CMPIN VTHIN CMPOUT_N CMPOUT_P 0.1u CMPA_P VTH2 GND PAout[1..12] TPout1 J2 TPout R59 i SE50 1 2 49.9R 3 5 4 6 S2 DL-Scint-SumAmp.SchDoc GND Repeat(A, 1, 12) DL-Scint-PreAmp.SchDoc R60 Molex 0733660030 J3 PAout7 PAout8 PAout9 PAout10 PAout11 PAout12 S1 S2 CMP2 DL-Scint-Comparator.SchDoc GND 61200621721 GND 49.9R SE50 R35 S3 S4 S5 S6 CMPB_N CMPB_P Sout2 PAout MCX output connectors for Test-out & pulser-in signals Repeat(PAout) Sout CMPIN VTHIN CMPOUT_N CMPOUT_P i 24.9R VTH1 1 Vtest TPout2 TPout R36 R37 DNF DNF 3 5 2 4 R38 GND J4 GND F1 5.1k 0.1% 1 2 1 +V +Vin 1 U7A GND +5V0 J7 U8 AD8639ARZ 0ZCJ0050FF2G 2 Molex 0733660030 2 C C 8 AD5694RBRUZ F2 R39 SCL 13 3 DAC-A DAC-B DAC-C DAC-D DAC-D 2 3 SCL VOUTA 1 2 3 SDA A0 A1 8 2 6 7 1 -V -Vin +Vin VTH1 SDA A0 A1 VOUTB VOUTC VOUTD 10.2k 0.1% 1 TPout1 12 14 3 4 0ZCJ0050FF2G 4 -Vin 4 9 10 R40 R41 3 2 5 4 GND LDAC RESET GAIN GND DAC-C -5V0 43045-0400 J5 15 +3V3 10.2k 0.1% 5.1k 0.1% GND GND 16 1 Vref 1 +3V3 RSTSEL VREF 1 J6 GND 11 Molex 0733660030 2 +3V3 +5V0 VLOGIC 2 R42 5 4 VDD GND GND 3 5.1k 0.1% 3 1 +Vin TPout2 +5V0 U7B 4 4 8 J8 -Vin R43 DAC-B 6 R44 3 2 5 1 4 1 7 A1 VTH2 +3V3 10.2k 0.1% 43045-0400 5 2k 2 2 GND GND D D R45 3 4 3 Title A0 R46 R47 DarkLight - Scint - Top C30 DAC-A -5V0 2k +5V0 GND 4 4 10.2k 0.1% 5.1k 0.1% GND 0.1u GND C31 C32 Size Number Revision Rev 0-A C33 +5V0 GND -5V0 GND +3V3 GND 0.1u 0.1u Letter TMM-102-01-L-D-SM 0.1u Date: File: 2-22-2023 C:\Work\..\DL-Scint-Top.SchDoc Sheet of Drawn By: DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 12 1 2 3 4

v2-- Prototype Scintillator May 2023 DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 13

v2-- Prototype Scintillator May 2023 Bottom Support plate--5mm thick --will be reduced in area Cooling Fan and possible compressed air flow DarkLight CM TRIUMF--May/June-2023 M. Hasinoff, UBC 14