Latest Developments in Integration and Validation of Data Flow Systems

The teams led by Phil, Kunal, Raul, and Pieter are working on various aspects of data flow system integration and validation. Progress has been made in implementing, testing, and refining different functionalities such as timestamp management, data conversion, formatting, and software verification. Challenges in triggering and error fixing are being addressed. The development includes creating test patterns, updating validation processes, and ensuring software robustness. Stay updated on the latest advancements and collaborations in this domain.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

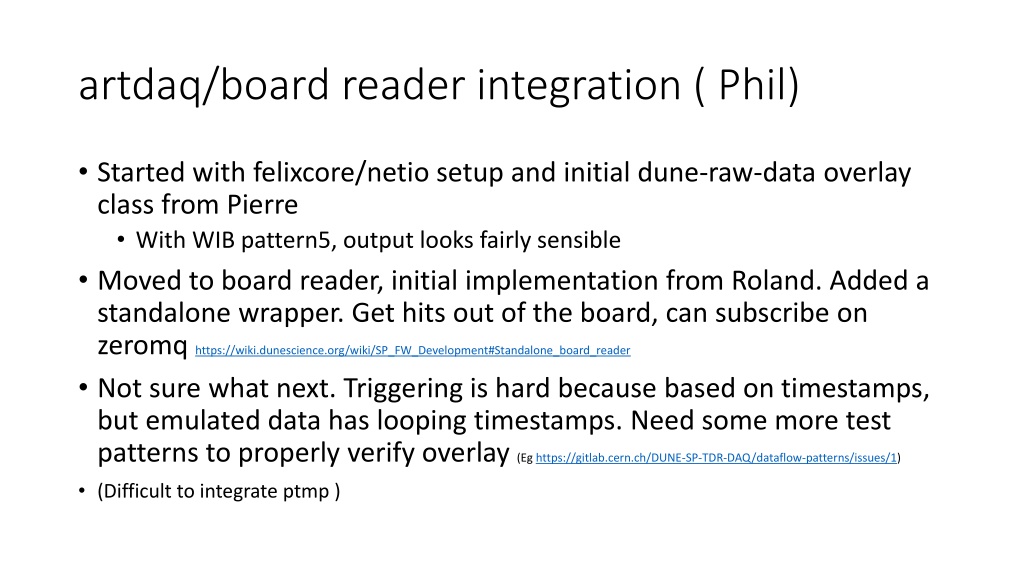

artdaq/board reader integration ( Phil) Started with felixcore/netio setup and initial dune-raw-data overlay class from Pierre With WIB pattern5, output looks fairly sensible Moved to board reader, initial implementation from Roland. Added a standalone wrapper. Get hits out of the board, can subscribe on zeromq https://wiki.dunescience.org/wiki/SP_FW_Development#Standalone_board_reader Not sure what next. Triggering is hard because based on timestamps, but emulated data has looping timestamps. Need some more test patterns to properly verify overlay (Eg https://gitlab.cern.ch/DUNE-SP-TDR-DAQ/dataflow-patterns/issues/1) (Difficult to integrate ptmp )

Validation Updates ( Kunal, Raul) TPG Validation Validation of Packetized TPG chain is done. Results agree. Had rounds of discussion with Raul and now converting the existing patterns into new python-framework files and adding new patterns. Found an error in packetization chain in LArSoft module. Fixing and reproducing the samples for state save and restore. ZCU102 Generated a bit file and programmed UoB zcu102 for full chain using Erdem s instructions. The 33b samples are ready to load into the design. Writing modifying the butler/wibulator scripts to load and read the data. ( Ongoing work ).

Verification Software Status Kunal, Raul, Pieter To-Do: Done: Timestamp management for Timestamp management for hitfile hitfile and and philfile philfile formats formats Philfile Philfile - -> WIB (objects) > WIB (objects) - -> 33B data conversion > 33B data conversion (A temporary measure to generate patterns for the full chain) All post HF formatting code is done and tested All post HF formatting code is done and tested Fix bugs in unpacker formatter Fix bugs in unpacker formatter and other formatters for a complete sw package (non-critical issues). (Another) channel mapping (Another) channel mapping to maintain header information in philfile- and hitfile formats. (Non-zero crate, slot, fibre header) Write documentation / user guide Write documentation / user guide Ability to read, write, and compare AXI4 Streams + Ability to read, write, and compare AXI4 Streams + arbitrator output arbitrator output Implement tests in CI Implement HF emulator in python and move away from hitfile format Tests for formatting functions have been developed and Tests for formatting functions have been developed and can be used in validating code can be used in validating code Move away from generating data in philfile format Continuous debugging of existing formatters and tidying of code Continuous debugging of existing formatters and tidying of code

FIR with State Save/Restore (Kostas) So far we ve been using a single 32-tap FIR implemented as a Xilinx IP Core State Save/Restore mechanism Store the last 32 data of an incoming packet for each channel Retrieve data and preload them into the FIR when it s time to process a new packet from that same channel Currently approach is to use 2 IP cores and ping-pong between them

FIR with State Save/Restore (Kostas) Design is currently under debugging Storing and retrieving data works correctly Main issue at this moment is to convince the IP core to hold once data is preloaded and not to start processing is as a separate packet.

Tests in Felix Hardware (Tony Earle) Worked with Alessandro Thea and Phil Rodrigues to get NP04-SRV-030 back to previous testbed standard, (issue #40) Tested out Phil s boardreader instructions, (issue #42) Still working on getting licenses sorted so I can help with simulation and build testing. Estimate unknown as I am not sure how operational Europractice and the vendors are at the moment. May pivot to documentation cleanup work to be useful

Arbitrator Tests (David) Wrote simulation test bench for arbitrator Tested 4:1 with files from Raul. Hits agree Built 5 * ( 4:1 ) : 1 arbitrator tree. 20 input files . Hits agree. Ready for tests in ZCU102 ( the hits from all four processing chains should end up in output )